Tool/software:

Hello,

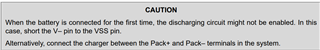

I am following the exact design as the BQ29700 EVM, and even using the same components. Every time the system is powered on (i.e. Cell is connected), I see a voltage difference between PACK- and CELL- for the first time. This causes the actual output voltage to be much lower than the cell voltage. I measure a ~2.7V potential difference between CELL+ and PACK-even when the cell voltage is 3.7V or higher (between CELL+ and CELL-). I am using the BQ29700DSER package. All the hardware components are new and show no signs of physical damage.

When I short CELL- and PACK- together, the voltage differences return to the expected values - i.e. Cell voltage matches pack voltage. This symptom is similar to original author's post.

As a potential mitigation, do you see any issues if a 5Mega Ohm resistor was connected directly between CELL- and PACK- ? Does this bypass the protection circuit instead? I am picturing the case when both FET gates are not driven and CELL- and PACK- have a high impedance path between them. Alternatively, do you have any recommendations to resolve this behavior?

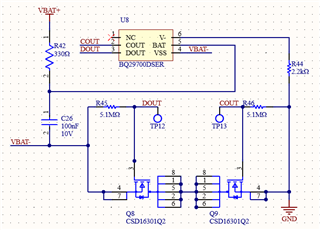

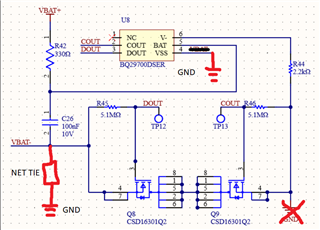

Please see attached application schematic below -