Tool/software:

Hello,

My name is Pritam. I am part of the semiconductor group at Google.

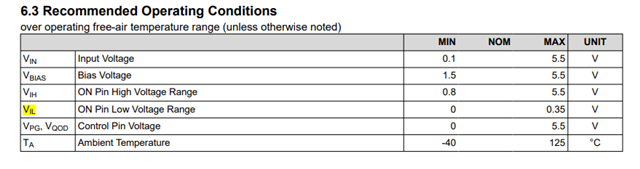

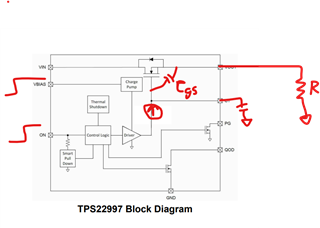

I am using TPS22997 load switch for one of eval board design for essentially creating a power-up sequence.

However, i am observing that when the load switch is biased (VBIAS = 5V is provided) and load switch is enabled (ON pin is HIGH) but with VIN (input) floating, there is leakage on the output.

I am providing 5V VBIAS to the BIAS pins. I am asserting the ON pin (HIGH) after VBIAS is provided to the load switch. But, the input pins (VIN pins) are floating...as in there is no input provided to the VIN pins yet.

During this state, i am noticing that the output pins (VOUT) is steadily increasing in level and it keeps increasing until i provide VIN (input pins are no longer floating) or I set ON pin to LOW (or remove VBIAS 5V).

Is this behavior expected of the load switch when the VIN pins are floating (with VBIAS = 5V and ON pin is HIGH)? The databook does not really specify the behavior in this particular situation. I understand that this may not be the intended operation of the TPS22997. But, i am trying to understand if this observation is expected.

And if so, where is this leakage coming from? Is this leakage coming from the VBIAS when VIN is floating (but VBIAS = 5V and ON pin is HIGH)? Thanks.

fyi: i have attached a small snippet of the connections to the load switch.