Tool/software:

Hello Team

We are trying to use watchdog within TPS65224-Q1 at Trigger Mode, the SOC is AM62A.

We set the WD_WIN1 as 0x13 which means the Twindow1 time interval is 11ms.

We set the WD_WIN2 as 0x4F which means the Twindow2 time interval is 44ms.

We feed the watchdog 30ms later after escape the long window, then feed the watchdog per 55ms. But the Watchdog reset the SOC only serval hundreds ms later.

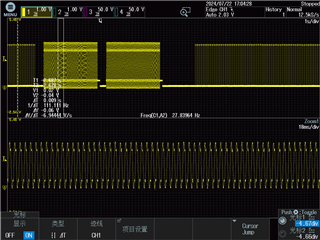

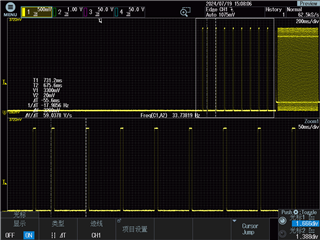

The waveform of the trigger pin showed as below. The upper half of the figure is the overview of the trigger pin, the lower half of the figure is the zoom view.

Could you help us to solve this issues please?

Best Regards.

Xianti