Tool/software:

Hi,

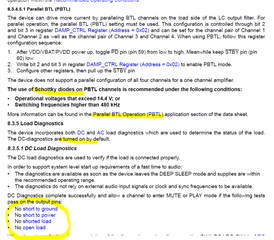

I am going to operate the device with

- 36V PVDD

- 480Khz

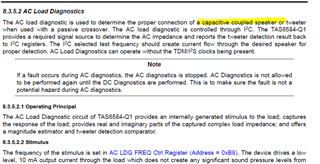

- capacitively coupled load with 1000uF bipolar capacitor

- PBTL on output 3 & 4 and 1 & 2 output not connected.

- 5-8Arms output capability

The EVm reference design doesn't include a Schottky diodes, could I please request the design sizing requirements for these diodes knowing the given above?

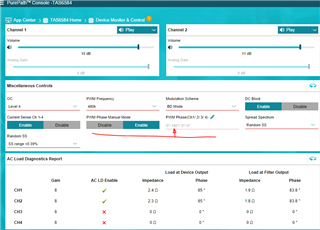

With PBTL configuration on 3&4 output (capacitively coupled) and an output pair not connected, how would the the device proceeds to Play mode if the DC or AC diagnostic is turned ON by default and test for open load?.

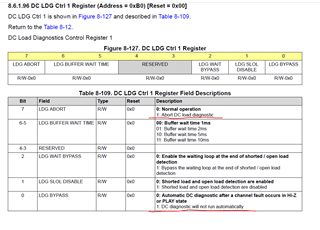

Is their a way to not test or bypass for open load during DC diagnostics?