Tool/software:

Hello all,

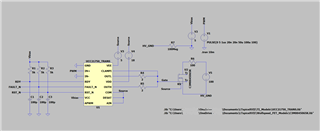

I am trying to simulate the UCC21750 Gate Driver on LTspice.

I have followed all the recommendations as given in the datasheet regarding the connections on this IC but so far I have not been able to get the model working. The simulation time is extremely long and I am not able to scope any signals.

I have gone through two other related posts but I did not see any resolution for this issue.

I have attached a screenshot on my model here.

I would really appreciate any help or recommendation.

Looking forward to your reply.

Best regards,

KKotsis