Tool/software:

Hi TI team,

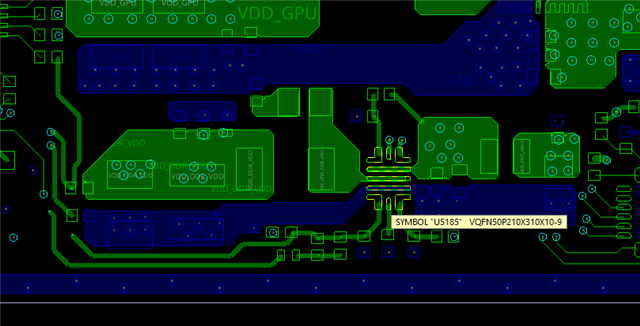

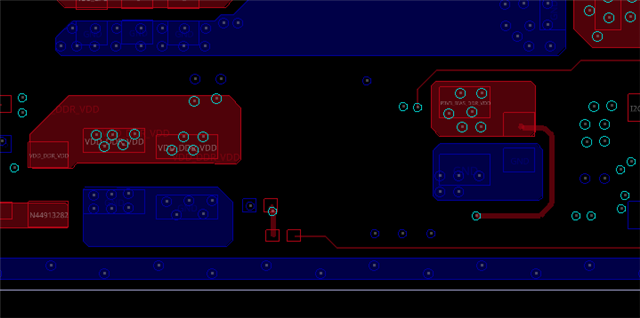

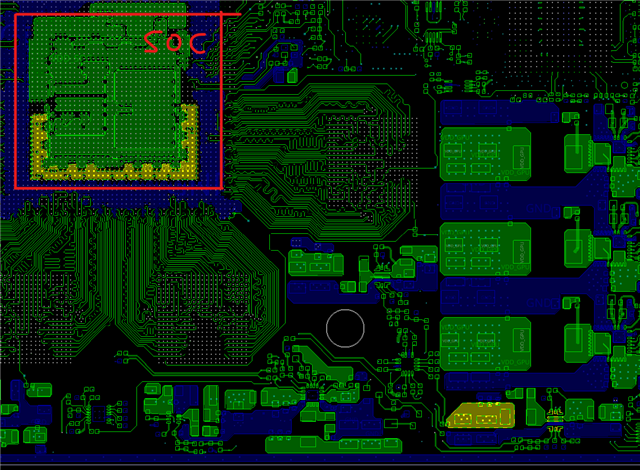

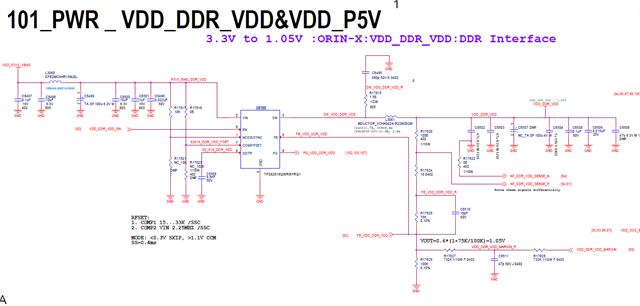

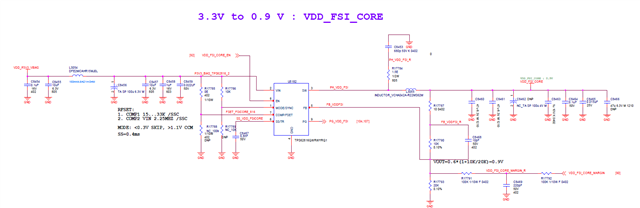

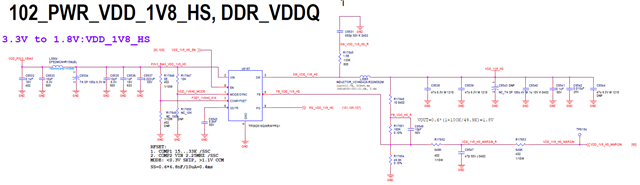

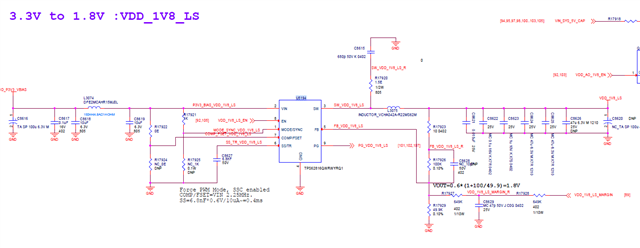

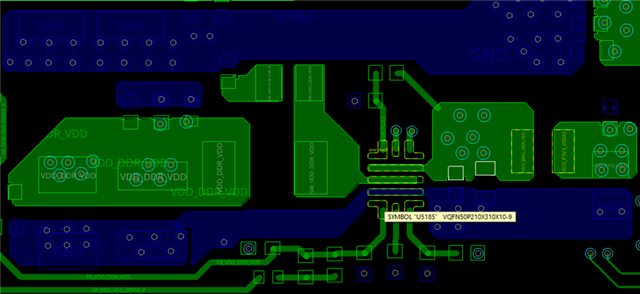

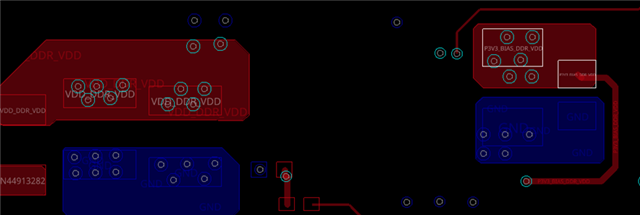

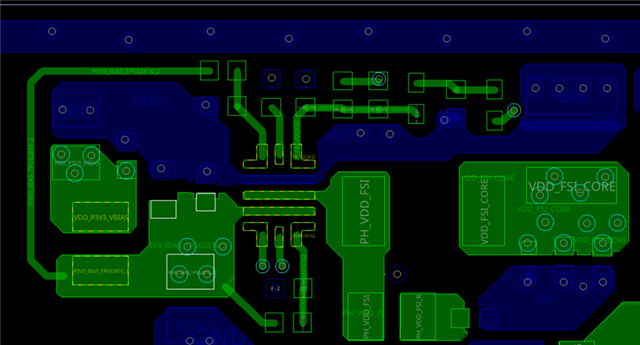

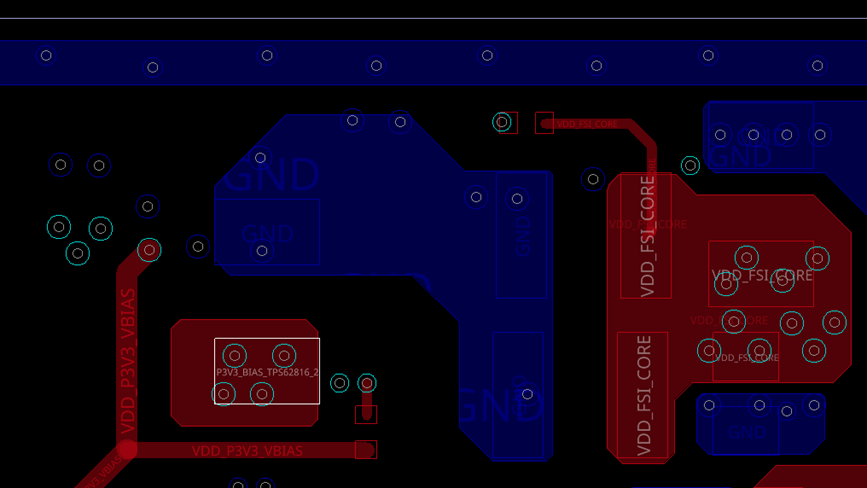

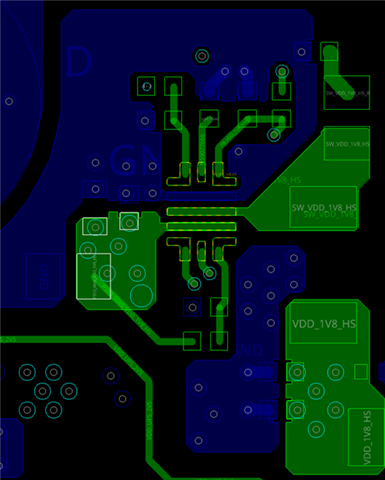

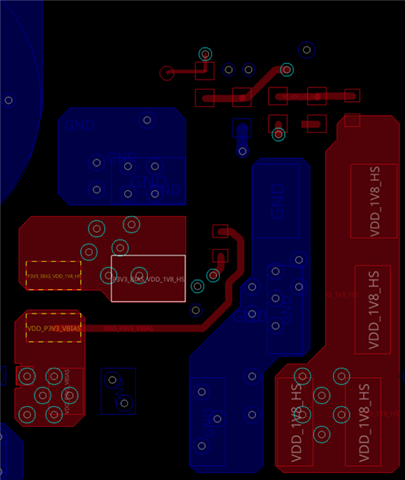

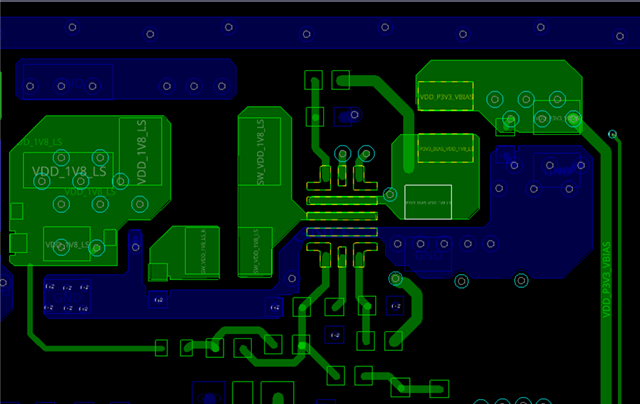

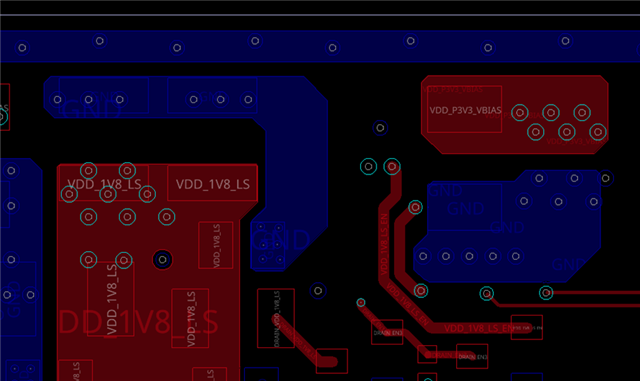

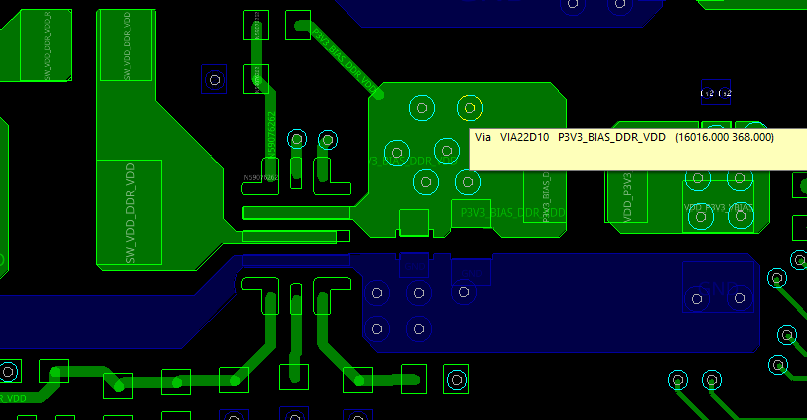

Here is schematic below,

Vin=3.3V

Vout=1.05V

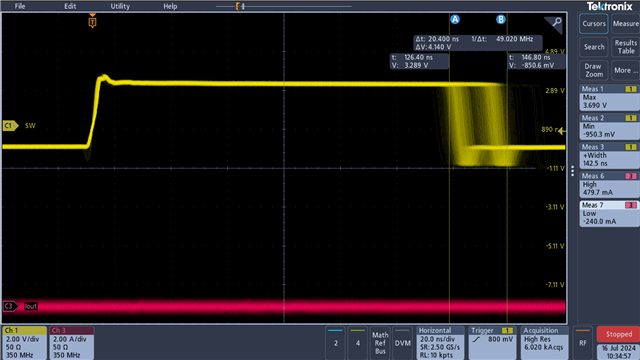

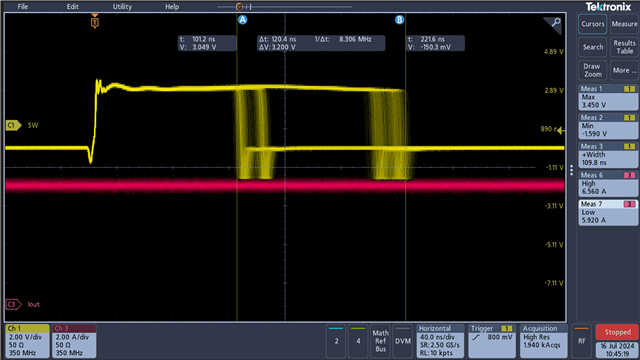

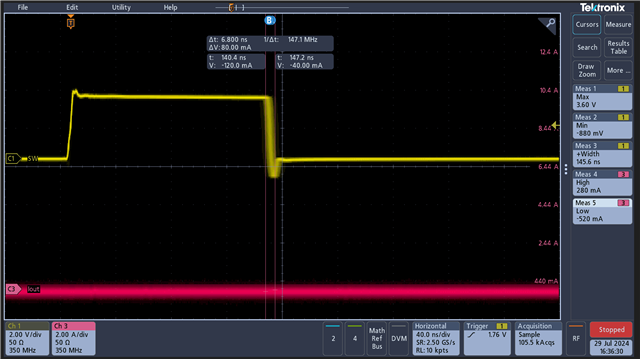

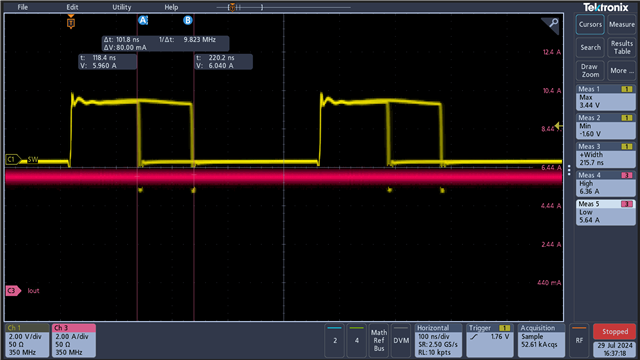

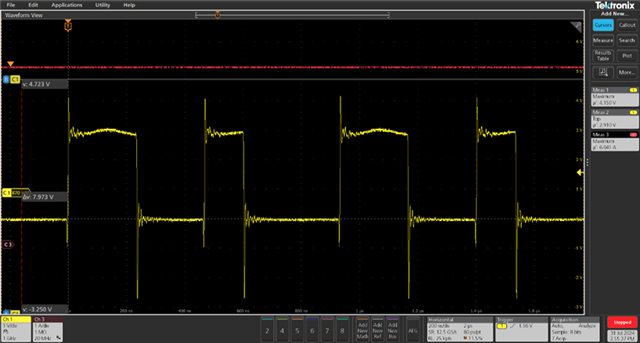

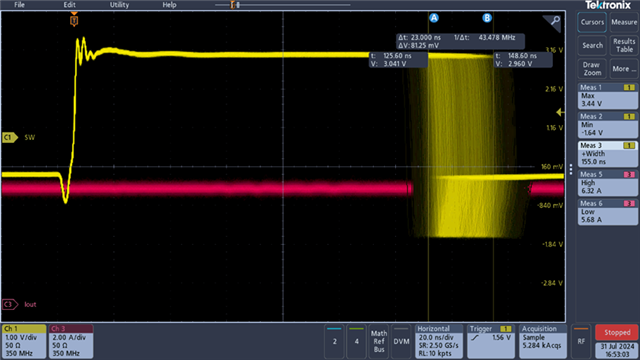

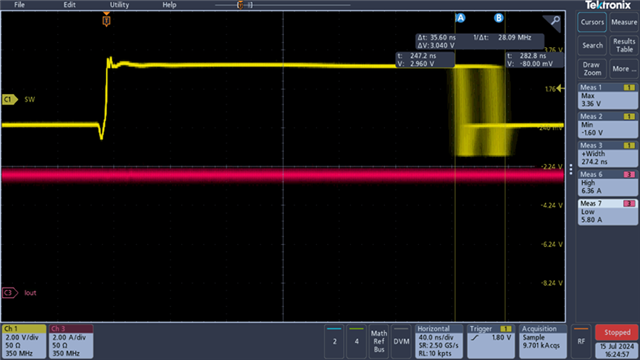

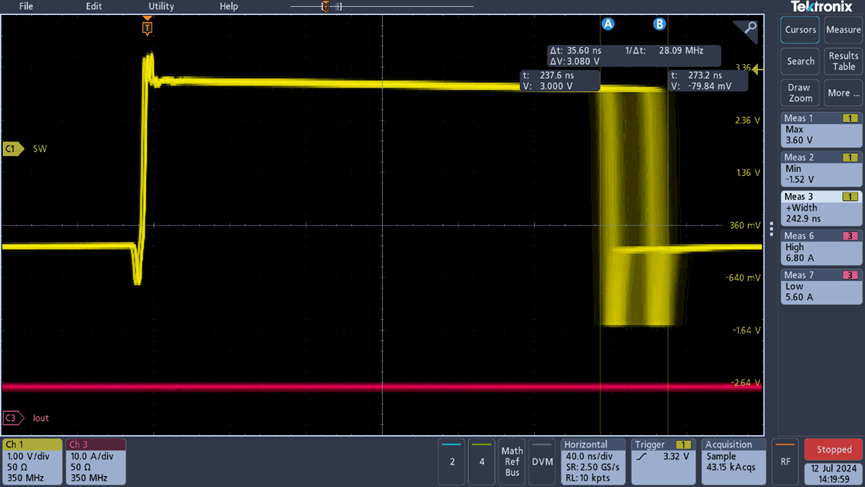

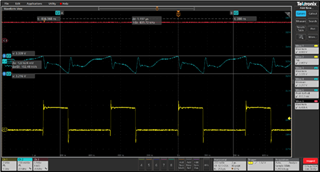

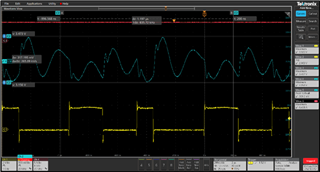

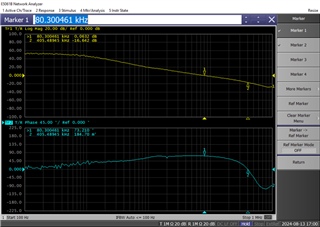

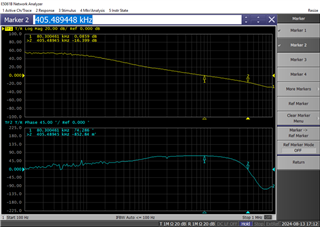

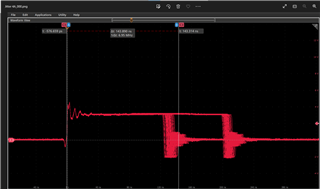

When the loading apply above 4A, the jitter shifts quite large. It looks like not a normal behavior.

I have checked my downsteam loading, and it is turn-off. Even when SSC is disabled, the phenomenon is still the same.

Do you have suggestion for this phenomenon? Thanks.