Tool/software:

HI!!

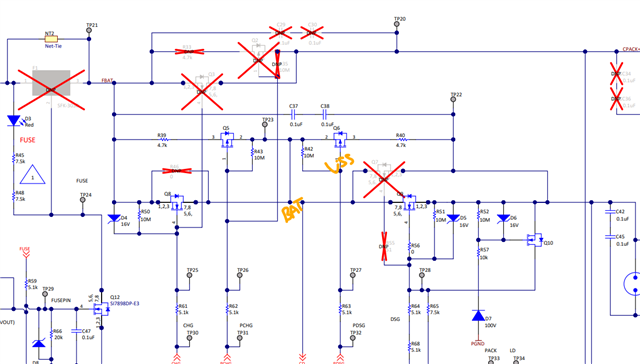

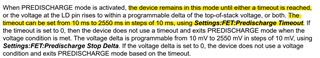

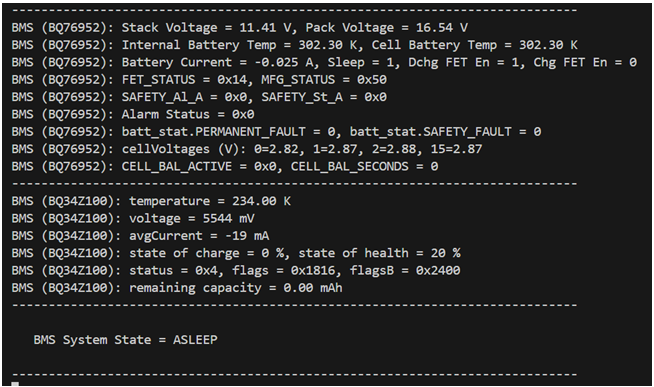

We are having an issue with charger detection while in sleep mode. Our BQ76952 device is transitioning to sleep mode automatically when the current is sufficiently low, which is the desired behavior. And when the device transitions to sleep mode, the CHG FET is automatically disabled, which seems fine. Then, when a charger is attached there is a noticeable PACK-TOS delta, but the device isn't waking up. See below screenshot in which the stack voltage is 11.41V, the pack voltage is 16.54V and the device remains asleep. We are writing 20 to the 0x9250 data memory register which is in units of 10mV, which means that the device should detect a charger if the PACK-TOS delta is greater than 200mV. But the device isn't waking up. The FET status register is reading 0x14, the 0x0057 MFG Status register is reading 0x50. There are no active faults. Are there other conditions that must be met to allow the device to wake up when a charger is detected via the PACK-TOS delta?

Thanks!

John