Tool/software:

Dear Dear,

I have two questions:

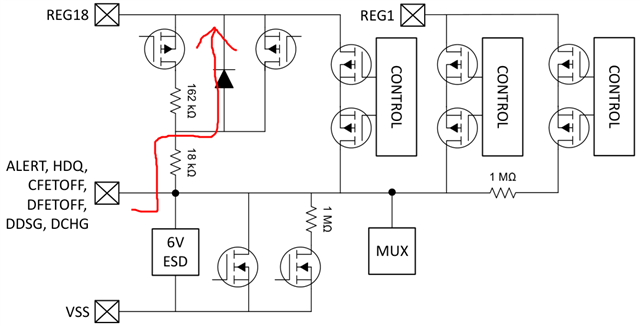

1. If 3.3V level output ports from MCU connect to PINs like CFETOFF/DFETOFF, will high 3.3V level cause leakage through the diode (or MOSFET's parasitic body diode)?

also, If ALERT is cfged as Open Drain output, out side 3.3V pull up resistance will also cause leakage through the diode?

so, the REG18 LDO could be unstable? at least Iq will be increased.

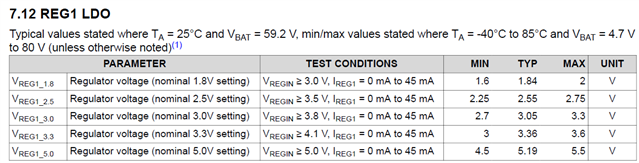

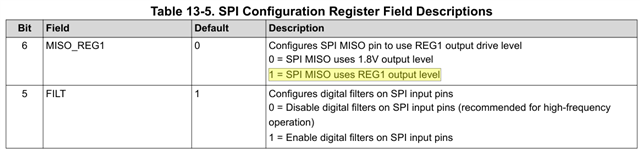

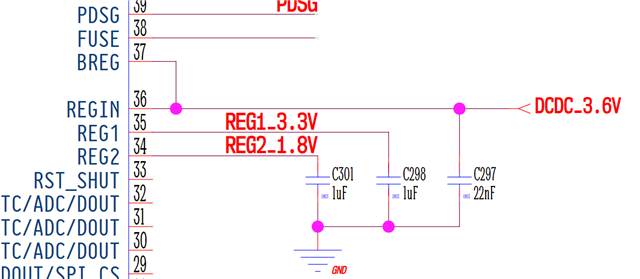

2. If REG1, REG2 is only configured as 3.3V and 1.8V, the external input 3.6V is OK or not to drive these two LDOs?

REG1 and REG2 wont' be taken too much current, maybe just for level shifting or SPI_MISO output level supply.

There is no voltage drop infos about these LDOs in datasheets.

That's All.

Thanks!