Part Number: UCC27424

Tool/software:

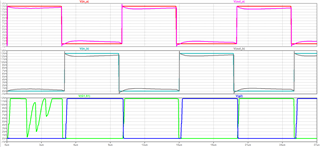

PWM pulses applied at the input terminals of UCC27424 have a deadtime of 325nsec, but the PWM pulses at the output terminals are overlapping. Can you please let me know why this is happening??

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: UCC27424

Tool/software:

PWM pulses applied at the input terminals of UCC27424 have a deadtime of 325nsec, but the PWM pulses at the output terminals are overlapping. Can you please let me know why this is happening??

Hi Shashank,

The UCC27424 does not have deadtime in the device. Do you mean that you are implementing the deadtime yourself? Can you provide waveforms of the two inputs and two outputs (at the pins of the driver)?

Thanks,

Rubas

Hi Shashank,

The deadtime on the output signals on the primary side look to be sufficient, but then it looks to be no longer sufficient on the secondary side. It looks like the secondary side output slew rate is slower, which causes the overlapping. It could most likely be because of the delays on the secondary side, so try to reduce the capacitance of C1 and C2, and see what the results are.

By the way, I see that you are using a push-pull topology to drive half-bridge. This app note may help in designing: https://www.ti.com/lit/an/slla602/slla602.pdf

Thanks,

Rubas

By reducing C1 & C2 capacitor value, the pulses at the start started overlapping each other.

Hello Rubas Khalid.. Thanks for sharing the document link. I have designed according to that and now I am getting correct pulses with correct deadtime. Thanks once again.