Tool/software:

Hi,

To sum up from CSD19535KTT: CSD19535KTT thermal calculation - Power management forum - Power management - TI E2E support forums,

Rθjc is Junction to Tab thermal impedance, could you confirm my model?

J stands for Junction,

T for Tab,

B for Board

Is Rθjc of 0.4°C correct to measure Junction temperature from the top of the Tab?

NB: the FET is solder to a copper inlay of 20mm x 25mm x 3mm

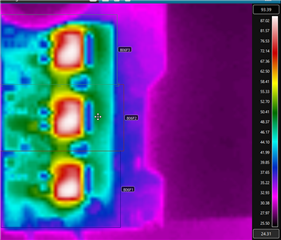

My goal is to survey the junction temperature during a stress test with a thermal camera on top (please see attached pictures IR and visible picture of the setup (3 FET on copper inlay 12mm apart)).

Kind Regards,

Vincent