Tool/software:

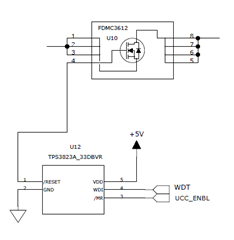

In the circuit shown above, I am attempting to use the TPS3823 in an industrial application to turn off the gate of a FET when /RESET is asserted, i.e. when /RESET goes low.

For terminology, let's call the WDI signal CLK when it is pulsing high or low (1kHz in my application). What I have found is that if WDI is kept high or low, the /RESET output is nominally de-asserted (high) and pulses low for a short time about once every 1.6 seconds. This does seem to be the intended operation of the device, but not what I need. I need the /RESET to stay LOW continuously when WDI is not getting a CLK signal.

Desired logic:

/MR L H H H

WDI X L H CLK

/RESET L L L H

I am going to try a modification of the circuit that is used to decouple the WDI signal (in the data sheet/3823A version) but I thought there might be an app note or circuit suggestion that I can use.

Thanks!