Other Parts Discussed in Thread: TPS3813-Q1

Tool/software:

Hi Team ,

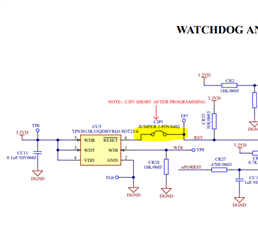

We are using ( TPS3813K33QDBVRQ1/SOT23-6 ) watchdog for voltage Supervisory .

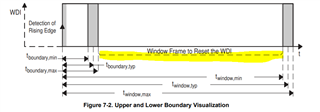

WDR and WDT pin are connected to VDD , so triggering pulse time on WDI pin is 20msec at interval of 2Sec .

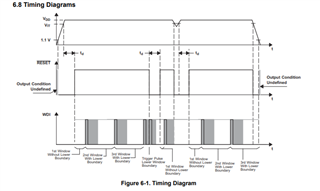

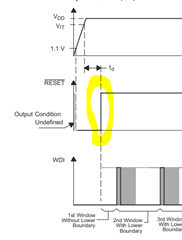

but before my MCU initialize watchdog IC sending resetting pulse .

can you suggest me what to do before initializing

or how to configure TPS3813K33 IC

Best Regards

Ankush Tiwari