Tool/software:

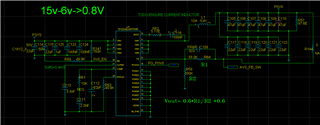

We are using part TPS54A24RTWR to generate core voltage in my design to Eth Switch IC, I try to run Webench and the results strangers

The core voltage should be very accurate ( Typical =0.8V , MIN=0.77V, MAX=0.83V).

additionally, my board is very dense so so I don't want to put unnecessary BOM.

the approach in my HW team is to add capacitance as much as possible but for now, I can't do it if it not necessary.

Vin= 15V(ignore the 6V)

Vout=0.8V

Iout=6A

if It's overdesign let me know, in addition I don't want to be close to margin so please consider it.