Tool/software:

Hello,

I would like to ask you a question about the TLC5940.

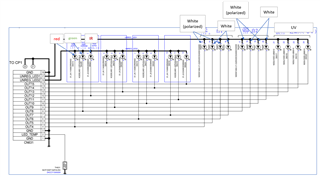

Each LED will emit light in fours. They will emit light in the following order:

1. White x 4

2. White (polarized) x 4

3. Red x 4

4. Infrared (IR) x 4

5. Green x 4

6. Ultraviolet (UV) x 4

7. White x 4

The following are the symptoms of the malfunction.

1.White: Lights up normally

2.White (polarized): One does not light up (D6303: OUT6)

3.Red: One does not light up (D6315: OUT6)

4.IR: Two do not light up (D6321, 6322: OUT12,13)

5.Green: Lights up normally

6.UV: Two do not light up (D6317, 6318: OUT12,13)

7.White: Lights up normally

Even though all four LEDs are controlled with the same settings, one or two of them do not light up.

The LED driver sends 16 channels of LED parameters all at once, turning on all four LEDs at the same time.

The above malfunction does not occur all the time.

It occurs about once every few times when the power is turned ON/OFF.

When a malfunction occurs, the malfunction symptoms will recur until the power is turned OFF.

Normal operation returns when the power is turned OFF and then turned ON again.

When a malfunction occurs, the same LED is always affected.

However, while it has been confirmed that the malfunction occurs on two prototype boards, the location of the LED where the light emission malfunction occurs differs on each prototype board.

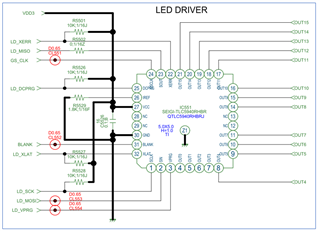

The circuit diagram is shown below.

There are two types of power supplies for the LEDs, as follows.

They are separated for each LED. The power supply is switched for each LED that emits light.

UNREG_LED1: White, white (polarized), UV

UNREG_LED2: Red, green, IR

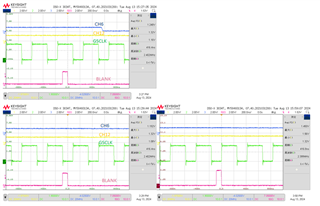

Below are the waveforms observed on a prototype board.

The relationship between GS_CLK and the BLANK signal is that a BLANK signal is inserted every 4096 GS_CLKs.

We were able to confirm that the phase of this GS_CLK and BLANK signal differs when the power is ON/OFF.

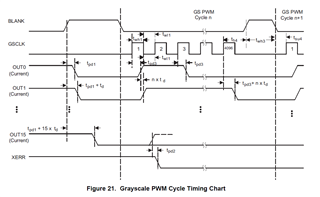

In Figure 21 of the datasheet, the phase relationship is as follows.

(Question)

Is there a possibility that a malfunction will occur if the timing "Tsu4" spec of 10ns or more is not met, or if the BLANK signal rises before 4096 times?

Are there any other reasons why this problem occurs?

Best regards,