Tool/software:

Hi Team,

We found the MOSFET of TPS92682 can be damaged when we are testing the supply voltage slowly rising condition.

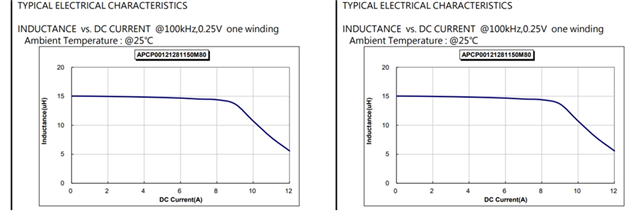

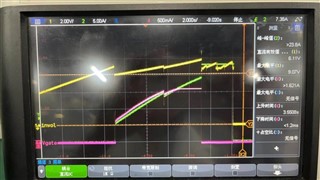

The slow voltage rising is from 0V to 20V, duration is 45s. When the supply voltage reached 6V, the TPS92682 started output(enabled), then it enters limp home mode. According to our configuration, limp home mode is 1A output current.

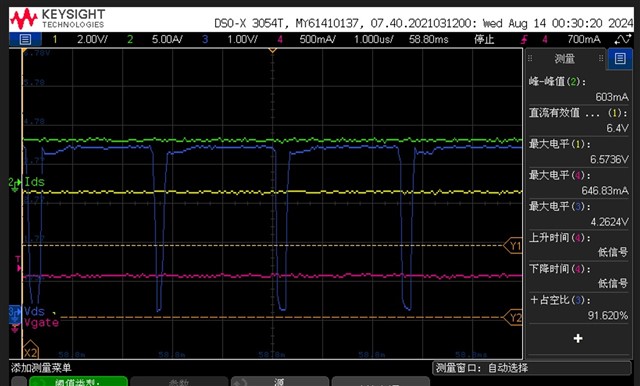

According to this waveform, it indeed entered the limp home mode, but output current and input current both rising slowly. And the output current reached 1.6A, input current increased to 20A as well. Then the MOSFET damaged.

We tested the Gate duty cycle at the waveform condition, the duty cycle is 92%, which is already the max duty cycle. And we suspect the MOSFET damage is due to high duty cycle.

Yellow=input voltage, green=input current, pink=output current.

We try to do some analysis on the efficiency,

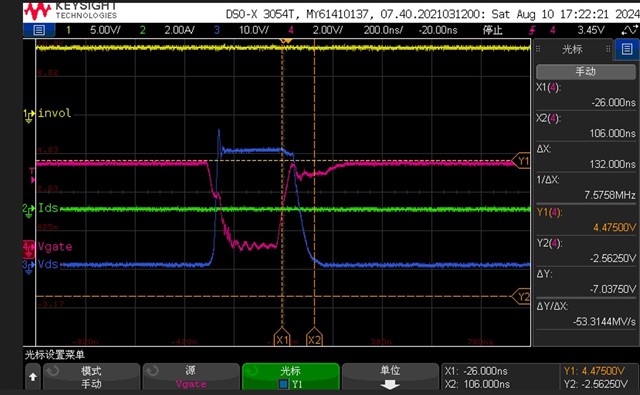

Here is another waveform:

Yellow=output voltage, blue=input voltage, green=input current, pink=output current

Based on this, we found the efficiency is around 56%, seems too low.

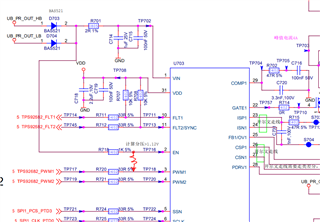

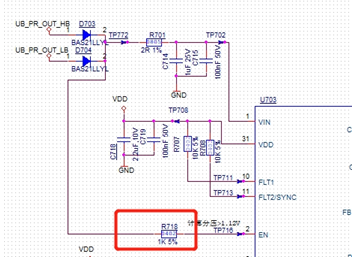

Here is the schematic if needed

Our questions are:

1. Why cannot the output current get to target 1A after the enable? Why there is a slowly rising on this current waveform?

2. Why it continues increase to 1.6A in limp home mode? Is it because loop control doesn't close?

3. When the input voltage is 6V, we tested the VCC voltage, it is 4.5V. Would this be an abnormal status?

Thanks

Best,

Frank