Tool/software:

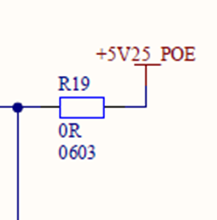

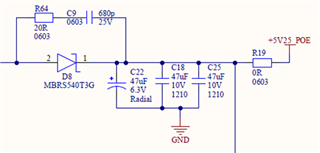

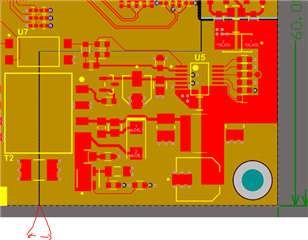

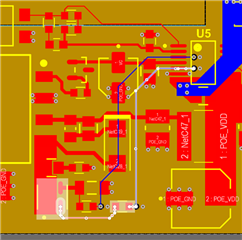

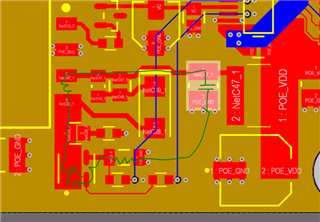

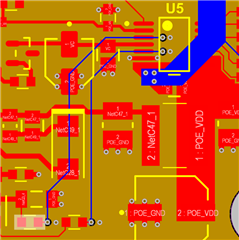

I just finished implementation of the TPS23753A, mostly based on the schematic of the TPS23753AEVM-001

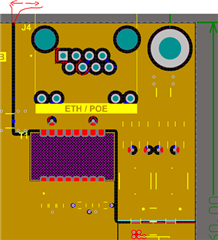

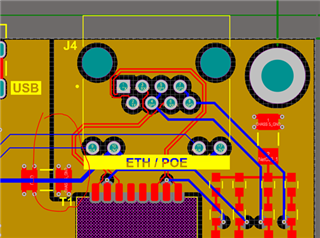

My stack-up is four layers and single sided assembly, so it differs a bit from the EVM lay-out.

Is it possible to get a review of the schematic and layout? That would help me out a lot and might prevent unneeded errors.

The files are confidential, so I prefer to send them by mail.

Thanks in advance,

Jesse