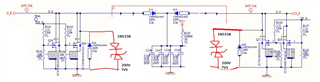

Other Parts Discussed in Thread: UCC28951

Tool/software:

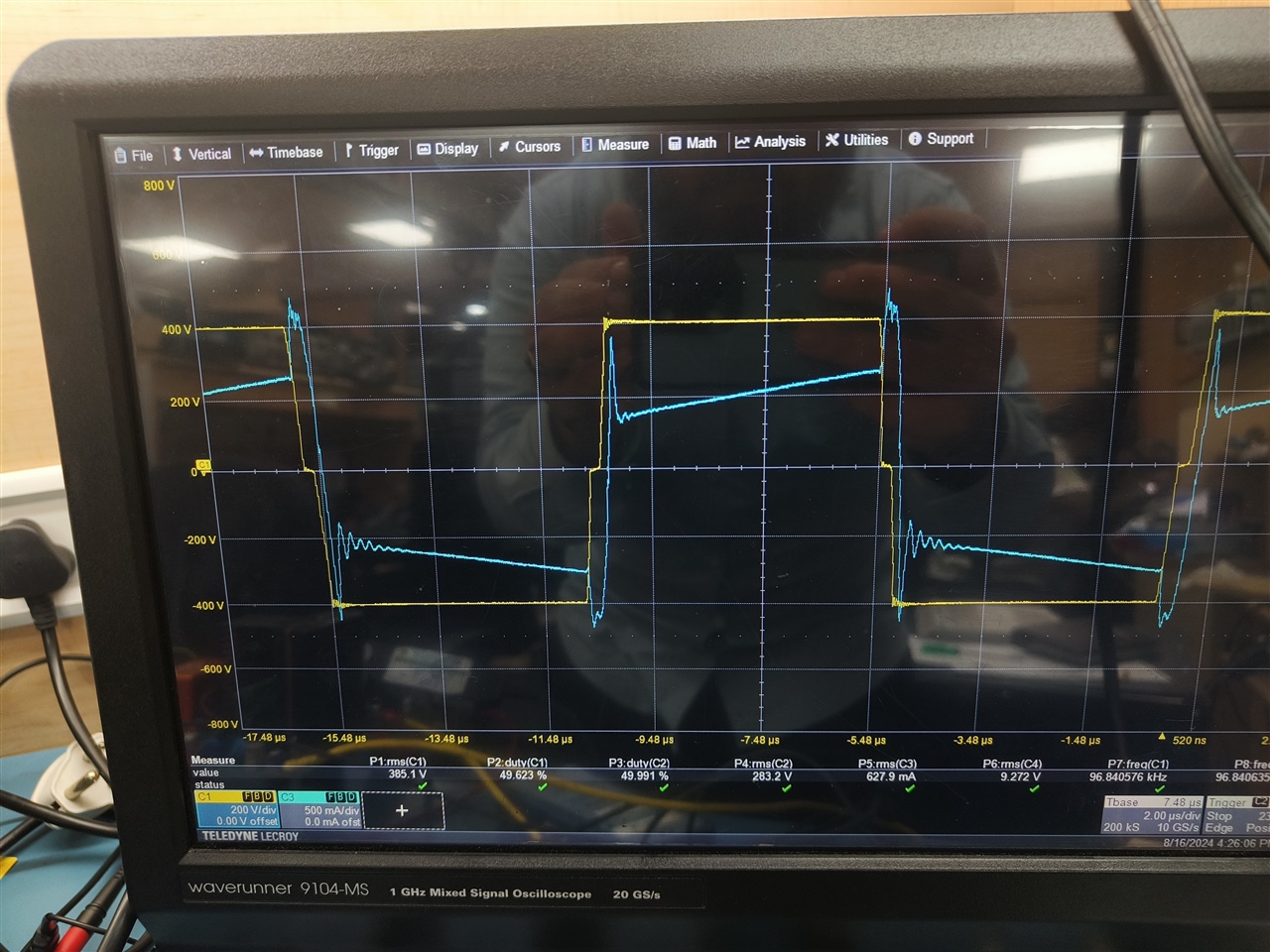

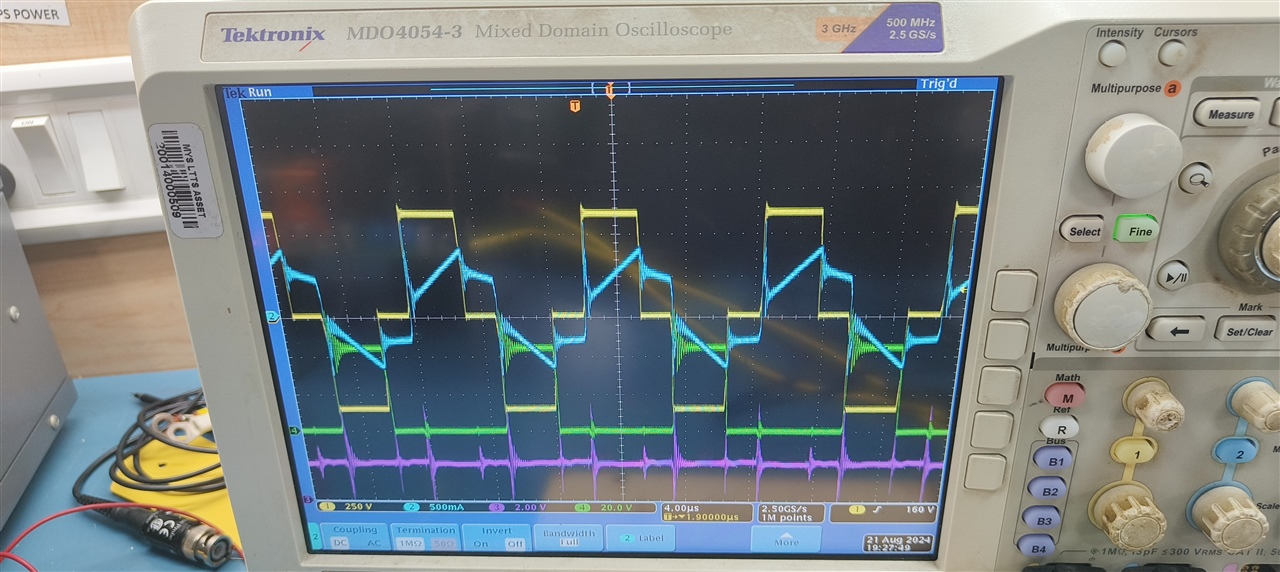

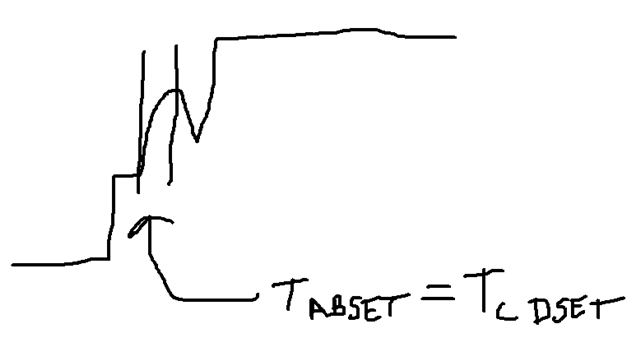

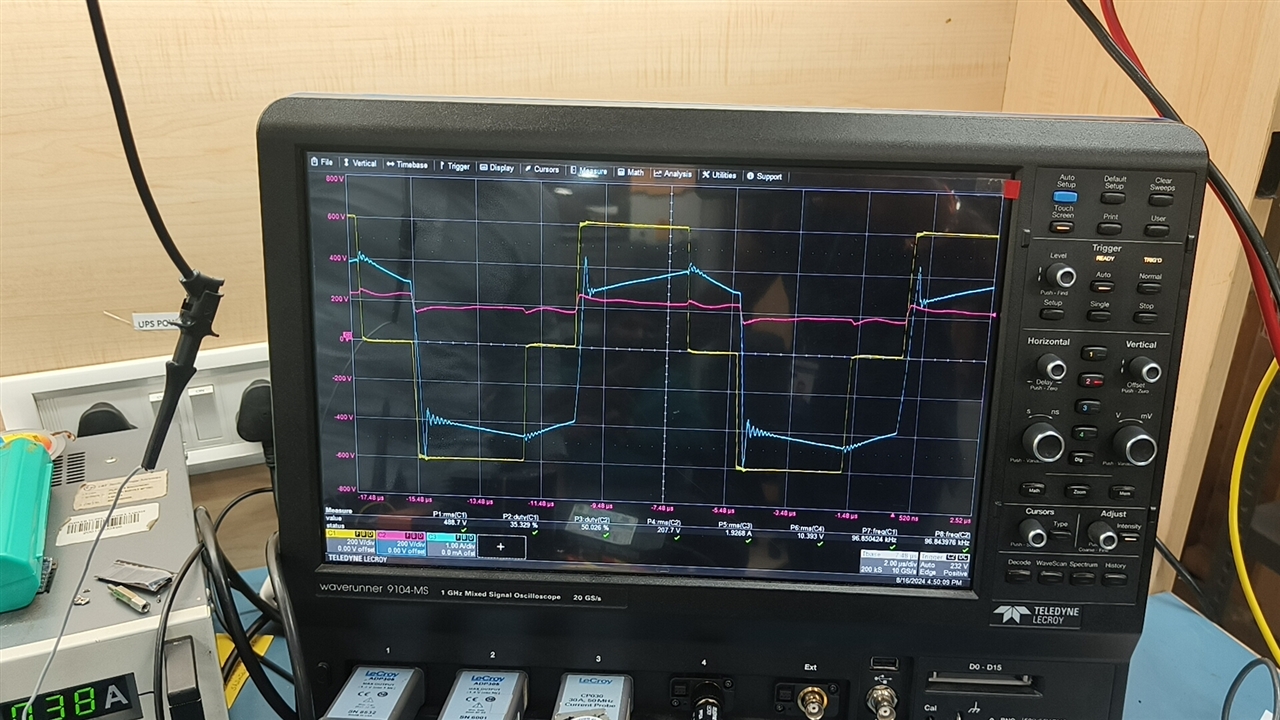

The voltage ring at transformer primary voltage is disappeared with reducing fixed delays.

FYI, TURNS RATIO : 27, Lmag: 8mH primary , Llkg :22uH

1. Vin : 600V, higher load currents , 20A and above

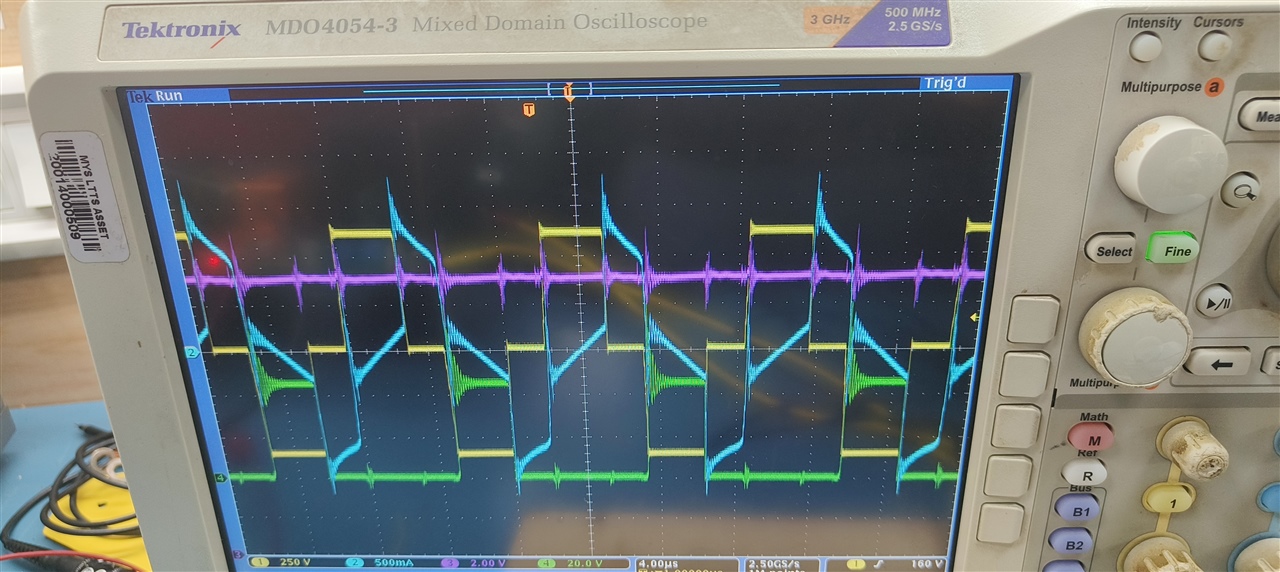

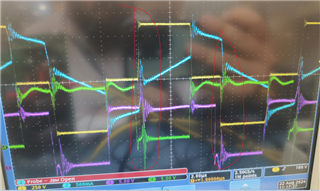

Yellow: primary transformer voltage

Blue : transformer primary current

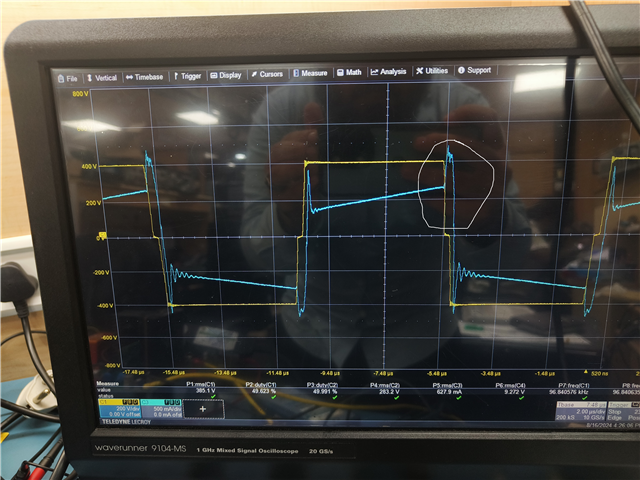

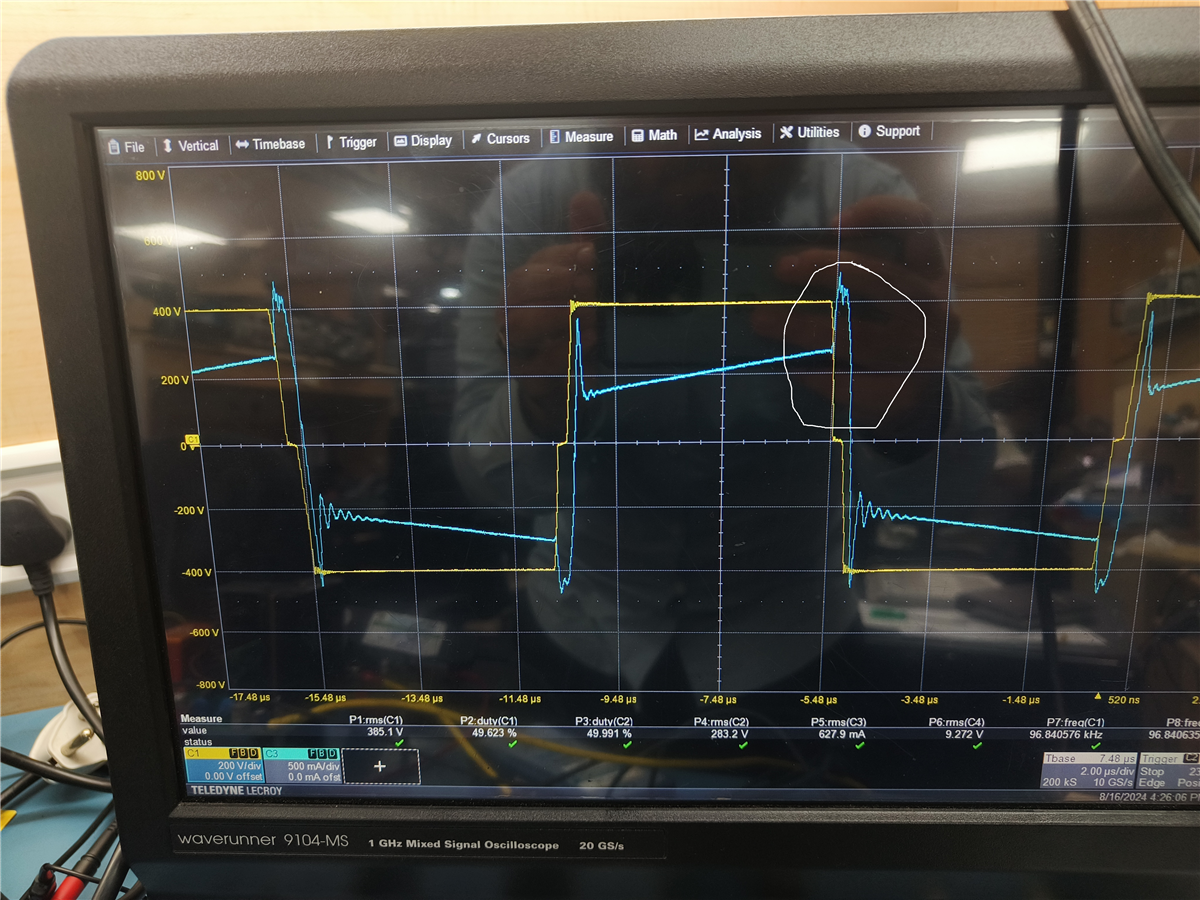

2. At lower voltages , for example at Vin :400V, 450V, load current:15A,

the current waveform at freewheeling period is increasing in other direction. Is it alright? Any reason why ? Is it due to low load current or high turns ratio ( 27 ) or anything else ??