Tool/software:

We are using TPS2373-4RGW for 10G POE Controller.

Kindly review the design and share your comments.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

We are using TPS2373-4RGW for 10G POE Controller.

Kindly review the design and share your comments.

Hi Aditi,

Thanks for reaching out.

I am not able to open your file in google drive. Could you please directly share it in E2E or let me know if you prefer to share via email?

Best regards,

Diang

Hi Aditi,

Thanks for your document. Please see the comments below:

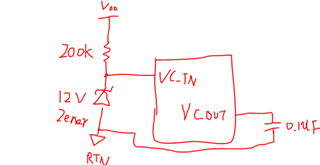

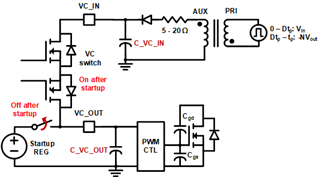

1. May I know if VC_IN and VC_OUT is needed in your circuit to start up the downstream PWM controller? If you do not need to use VC_IN and VC_OUT (and APD), it is more recommended to use TPS2372-4 instead of TPS2373-4. If you have to use TPS2373-4, you need to build a voltage divider circuit at VC_IN and a cap at VC_OUT as below.

2. The resistor of AMPS_CTL needs to be higher power rated (R226 used 0402). 1210 or larger size is recommended.

3. The input cap between VDD-VSS needs to be 0.05 – 0.12 uF. Normally 0.1 uF is recommended.

4. The output cap between VDD-RTN normally needs to be >68uF for Class-8 PD.

Best regards,

Diang

Hi Diang,

We need to use TPS2373-4, as we are using one of our existing design.

And for input cap, previously we placed 2.2uF but after no mounting that cap we tried to turn on the board from POE by using POE injector TPE-319GI from Trendnet and POE90U-1BT-X from Phihong then it was working fine.

Hi Aditi,

Thanks for your reply.

Please do not mount a big cap like 2.2uF at VC_IN in your case that VC_OUT is not used. You can make VC_IN cap 1nF or not mounted, and VC_OUT 100nF in your case.

TPS2373-4 has a trick in VC_IN and VC_OUT cap. Since VC_OUT has an internal start up voltage regulator. You need to make VC_OUT cap 10 times larger than its VC_IN cap. So that, when VC switch turns on and VC_IN - VC_OUT caps get shorted, the VC_OUT voltage won't drop below UVLO.

Best regards,

Diang

Hi Xing,

Noted. Thanks for your support.

We will place 100nF at VC_OUT, as per your suggestion.

Hi Aditi,

You are welcome! I will close this thread for now. Please reply or open a new thread if you have further questions.

Best regards,

Diang