Tool/software:

Dear Specialists,

My customer is considering LM61480 and has a question.

I would be grateful if you could advise.

---

I am currently designing a peripheral circuit for the LM61480.

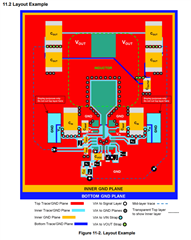

According to the LM61480 data sheet P.50 11.2 Layout Example has a GND pattern directly under L1.

It is generally considered better to remove the GND directly under it.

Is it correct to say that the LM61480 recommends that the pattern directly under the inductance be filled with GND?

Is there any problem with a GND pattern directly under the inductance?

---

I appreciate your great help in advance.

Best regards,

Shinichi