Tool/software:

Hi, we have just recently switched a LDO part from a MAXIM MAX8860EUA28 to a TI LP3982IMMX-ADJ/NOPB (as per the compatibility claim in your datasheet).

The circuit was misbehaving and after probing around we realised that there is a problem with the /FAULT pin which is not handled correctly on start-up.

It would appear that we cannot use the recommended MAX8860 TI alternative for cascaded power rails.

Our circuit consists of the following:

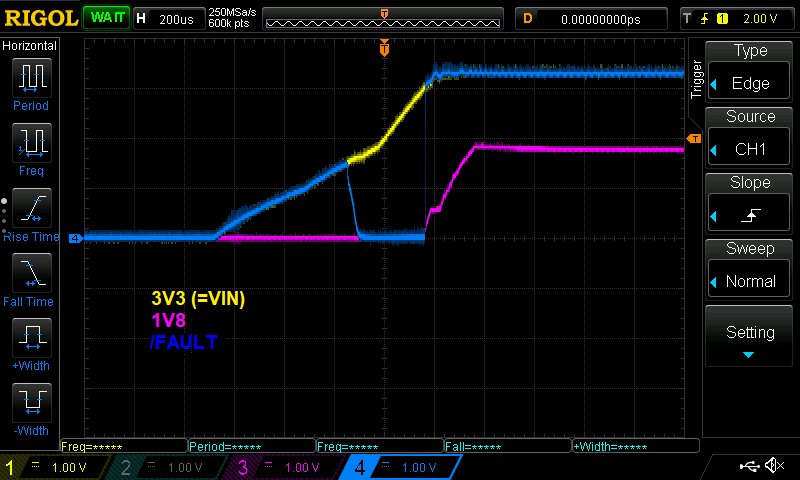

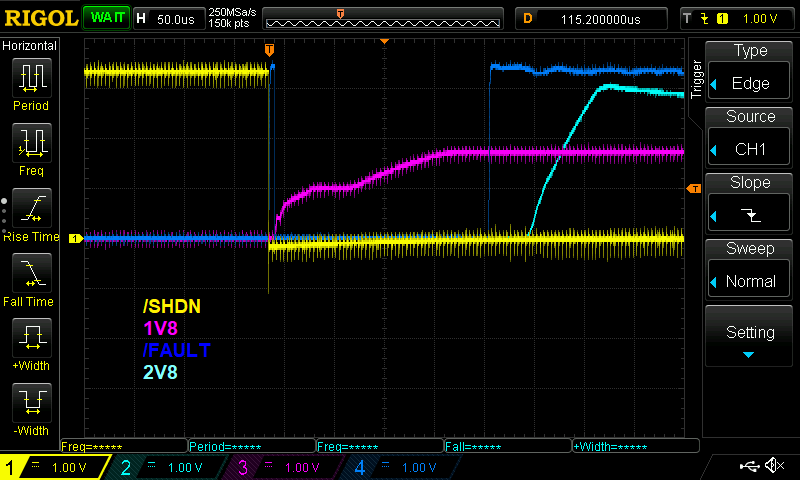

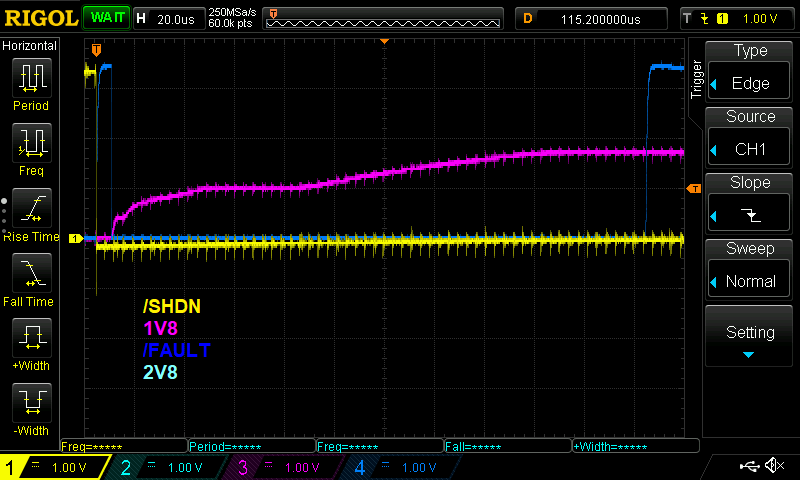

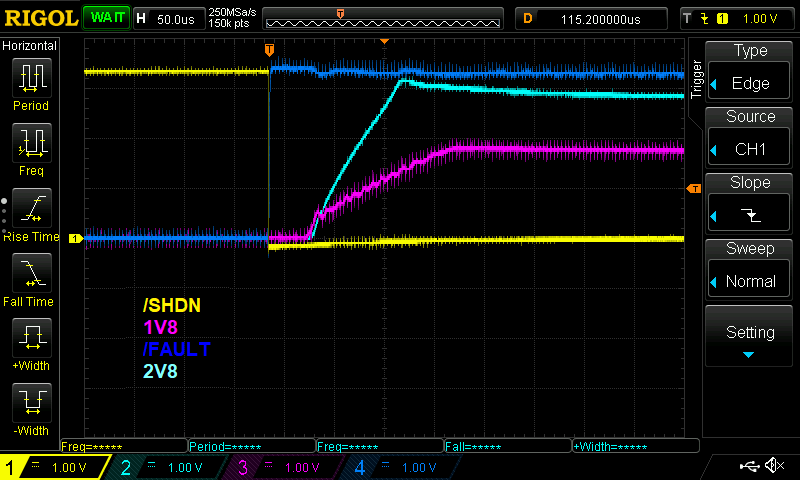

3V3 (always-on) feeds two LDOs, one for a 1.8V rail and another one for a 2.8V rail. 1.8V needs to start before 2.8V, so we cascaded them by having the /FAULT pin of the first LDO (1.8V) connected to the /SHDN pin of the second LDO (2.8V)

The first LDO (1.8V) is controlled with a software driven output connected to the /SHDN pin

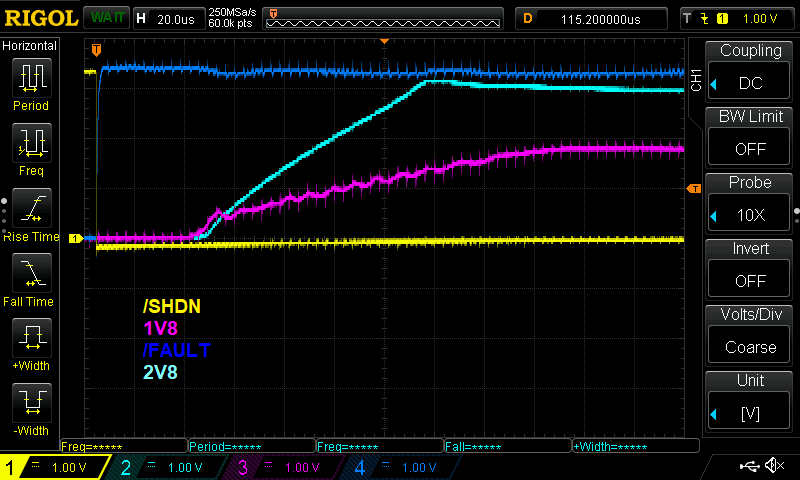

The circuit was validated with the Maxim chip and attached are the waveforms of a typical power-up sequence. You can see that the second LDO (2.8V) does not start before the first one (1.8V) enters regulation.

Now with the TI chip in place, we obtain a very different behaviour. Both LDO's power up at the same time. The /FAULT pin does not reflect the state of the 1.8V regulation.

We bought these chips from a reputable distributor and the chip marking is:

28NO

LEVB

Could it a silicon bug with that particular batch? Or a general limitation/incompatibility with the TI chip?

Regards,

Arnauld