Tool/software:

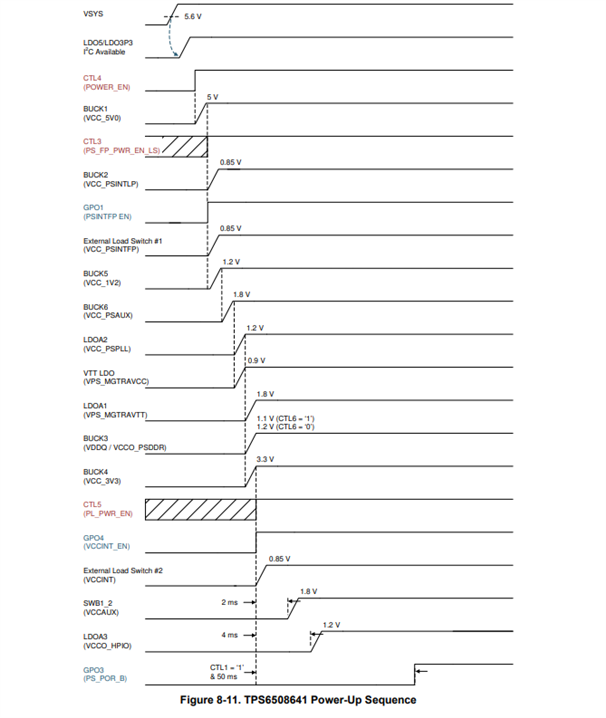

We are using TPS6508641RSKT in our design. We have connected a push button switch to pin CTL1( PMIC implementation is as per document scea113,fig 6.1).We want to know if we can use a AND gate output to the CTL1 pin. input to the AND gates to be PS_POR_PB_B and VCCINT_PG(frpm buck). Would this be ok? Any failure on buck providing 0.72V can result in reset of PMIC. Would this be beneficial for the design? Please let us know.