Tool/software:

We are looking for the below parameters of TPS74612PQWDRVRQ1 for signal integrity simulation:

Lslew(nH)

Rflat(mOhm)

Lout(nH)

R0(nH)

TPS74612PQWDRVRQ1 is used in this design for generating 1.2V and 2.5V for DDR4 interface.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

We are looking for the below parameters of TPS74612PQWDRVRQ1 for signal integrity simulation:

Lslew(nH)

Rflat(mOhm)

Lout(nH)

R0(nH)

TPS74612PQWDRVRQ1 is used in this design for generating 1.2V and 2.5V for DDR4 interface.

Hi Asif,

So sorry for the delay. Can you please describe the parameters you need in more detail? I think the Lout and R0 seem relatively straightforward (I'm thinking a first-order-approximated supply output impedance), but I'm not sure about the Lslew and Rflat parameters. Which software package are you using for your signal integrity analysis?

Thanks,

Nick

Hi Nick,

Thanks for your response.

We are using Ansys SIwave for signal integrity analysis. Ro and Lout are output resistance and inductance respectively.

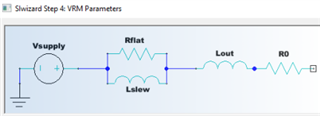

Lselw and Rflat are used to model the transient behavior of the VRM.

Typical equivalent circuit snap from the tool is attached here for your reference.

Related article on this VRM modeling: - Design a VRM with perfectly flat output impedance in 5 seconds or less - EDN

Regards,

Asif P N

Hi Asif,

The parameters are the following:

| Rout | 21.3mΩ |

| Lout | 16.3nH |

| Rflat | 23mΩ |

| Lslew | 260nH |

TPS746_output_impedance_300mA.xlsx

Regards,

Nick