Tool/software:

Hello,

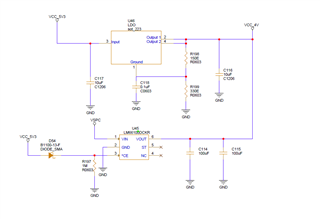

We are using LM66100 ideal diode in our application. We have used this chipset for OR-ing of two supply voltages.

Below are the power rail information for which we have done OR-ing.

1. 4V output voltage comes from LDO output.

2. 2.7V-4.2V output voltage which comes from supercapacitor backup voltage (This power we have switched through the ideal diode while input power disabled.

Below is schematic diagram of logic we implemented.

Working of circuit:

When input power is present the ideal diode is turned off: VCE-VIN= 5.3V - 4.2V (Supercap voltage)> Turn ON threshold limit (80mV). In this case output circuitry will take power from LDO.

When input power is absent the ideal diode will be turned on: VCE-VIN= 0V-4.2V (Supercap voltage) > Turn OFF threshold (-80mV). In this case our output circuit will take power from supercap through ideal diode.

This logic works fine in lab testing with number of turn ON/OFF cycles as well. But in some unknown scenario and cases the ideal diode gets permanently damaged.

One of the known reason we found is we observed CE pin behavior on DSO and its too much sensitive to the noise in the presence of 1M ohm pull down as well. So that is know reason. To overcome this we have added 0.1uF capacitor on CE pin and we observed noise gets reduced by adding capacitor.

Still we are facing this issue of permanent damage of ideal diode, where we have observed that input and output of ideal diode is getting shorted.

So kindly help us to resolve the issue, We are in mass manufacturing of the boards and 10% is the rejection due to this ideal diode chipset.

Thanks,

Akshay Damare.