Tool/software:

This has been kicking us in the butt for a while so, here i go........

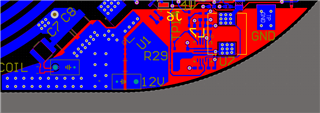

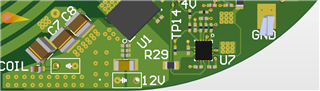

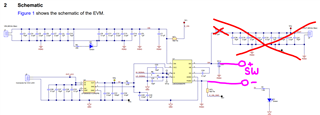

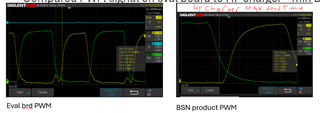

- We are designing a new product that uses the LMG5200 to drive an LC tank at resonance.

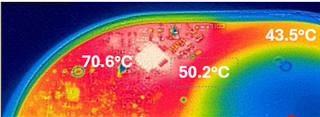

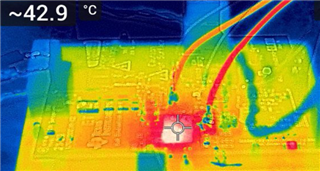

- When putting out ~ 6-7 Watts of power we see excessive heating in the order of 70C on the IC.

- When driving the same load and same power output using the Eval board we see around 40C.

So our natural question is, what’s causing the heating difference. We have tried a few board iterations and have reduced the temp by 20C but we still far off from the eval board.