Tool/software:

Hi,

I am using TPSM84209 for a 0.4 A application. Input voltage is 15 V and output voltage is 5 V.

1- I have a 100 uF electrolyte and a ceramic 100 nF near the pins of the IC. Do I need to increase the size of the ceramic capacitor? I thought with having only 0.4 A, the ripple in the input cap is small and does not need to be size higher.

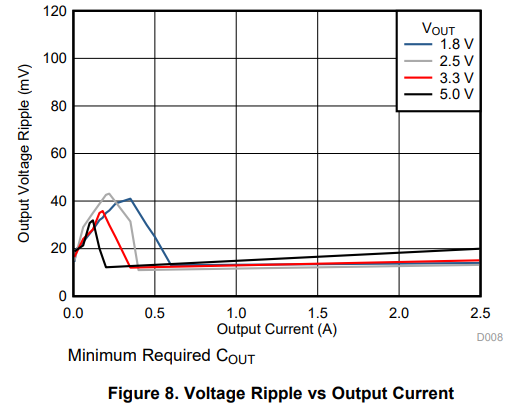

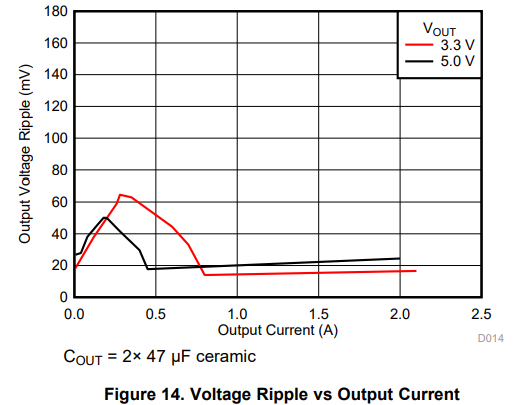

2- Will pulse skipping happen with these specs? In the graph in the datasheet, it looks like pulse skipping will happen for any current with these voltages.

3- Does pulse skipping result in output voltage overshoot?

4- What size of copper plane do I need given that we have ~0.3 W of power dissipation? In the datasheet, 63mm*50mm is mentioned.

Thanks,

Marzi