Tool/software:

Hi team!

Could you please help with below six questions from my customer?

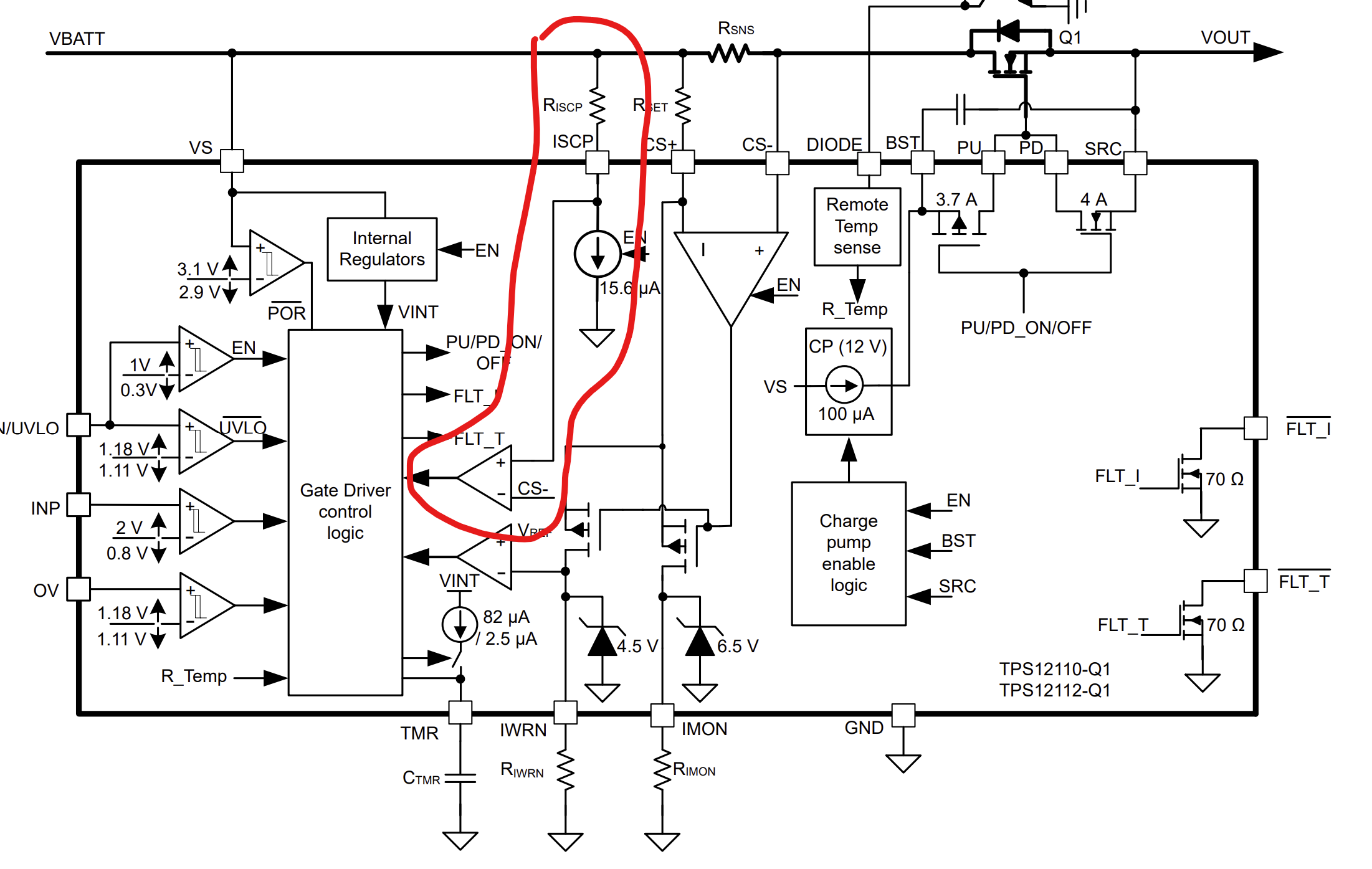

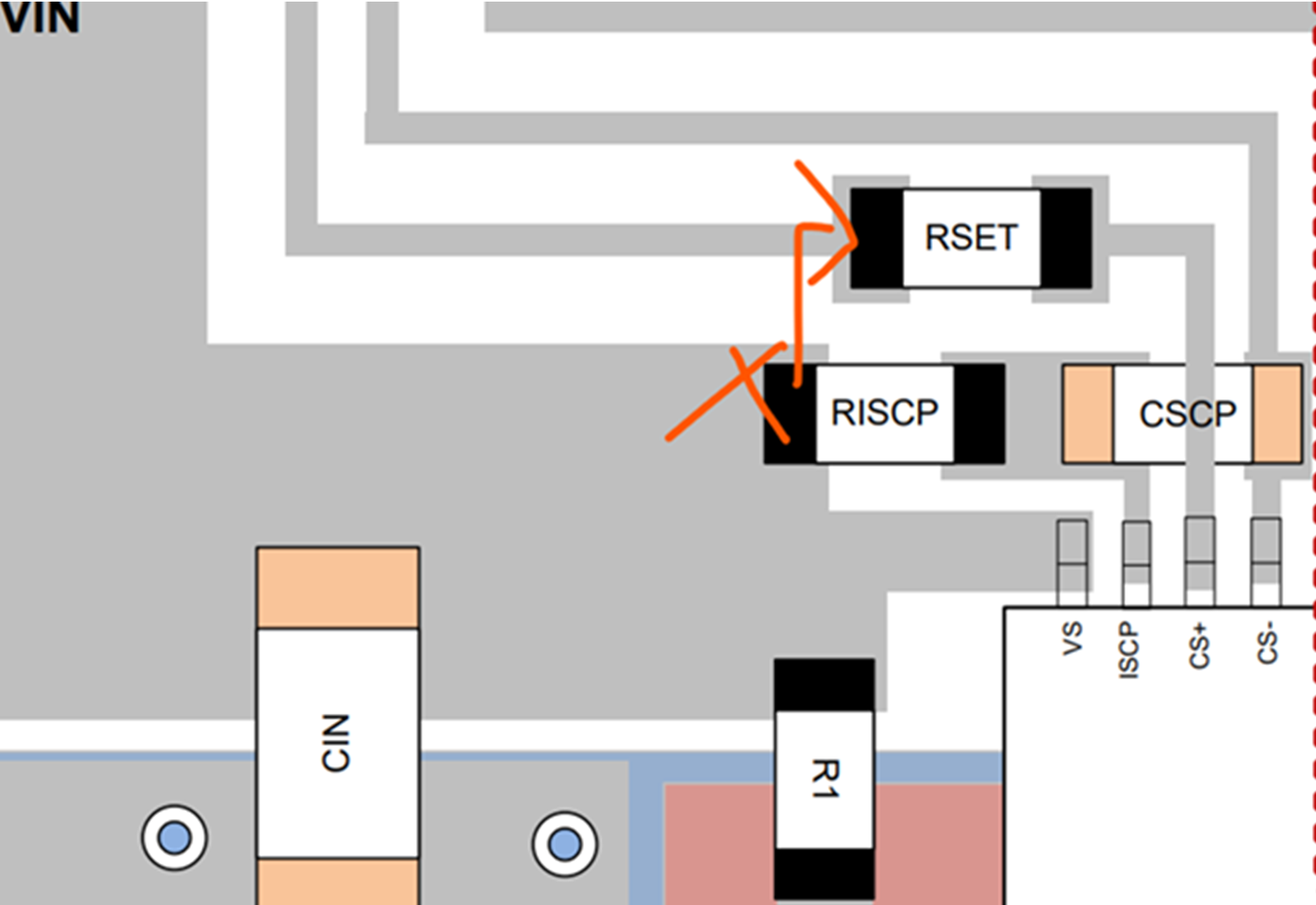

- What kind of failure mode will TPS12110 cause if Rscp is open or shorted?

- What kind of failure mode will TPS12110 cause if Rset is open or shorted?

- What kind of failure mode will TPS12110 cause if Rimon is open or shorted?

- What is the voltage limit range across Rscp?

- The range of I(iscp) is 13.7uA-17.6uA. In our current application scenario, the error of the short-circuit protection point is ±30A. Is there any way to reduce the fluctuation of I(iscp) and improve the protection accuracy?

- Is the ±200uV deviation of V(OS_SET) a random deviation? Why is +200uV used in the application example in the datasheet?

Thanks!

Best Regards

Josh Wei