Tool/software:

Hi team,

My customer is using our LP876242-Q1 and looks at our reference design.

And they have two questions about our reference design:

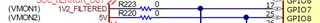

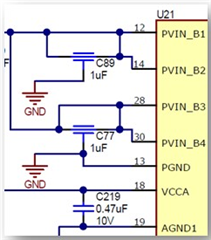

1. Why should PIN17 and PIN25 of PMIC be directly connected to 1.2V and 5V power supply? Datasheet defines these two ports as normal GPIO I/O.

2. What is the role of Murata NFM18HC105C1C3 in the reference design? Why is this particular capacitor chosen?

Thanks a lot!

Best Regards,

Matt.