Tool/software:

Hi,

I have recently been testing a phase-shifted full bridge design using the UCC28950 chip. It is a standard design implementation of the chip using PCMC.

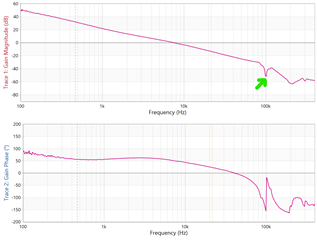

In the open loop-response, there is a sharp drop in gain at the switching frequency (100 kHz) as seen below:

This appears to overlay the normal PCMC sub-harmonic peak at half the ripple frequency (100 kHz), as you can see the gain start to flatten out as it approaches 100 kHz.

This is also visible in the UCC28950 EVM open loop response bode plot, seen below:

I am wondering if this is standard behaviour? And if so, what causes it?

Thanks,

Niall