Tool/software:

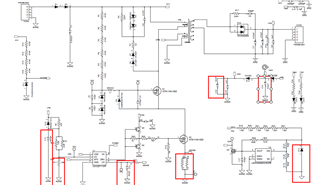

Hello! I have created an SMPS based on the document "400- to 690-V AC Input 50-W Flyback Isolated Power Supply Reference Design for Motor Drives."

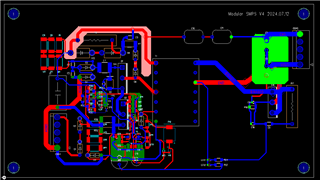

The schematic is as follows, and the PCB layout was done in the same way.

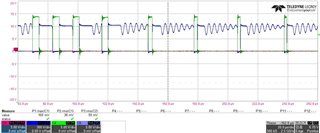

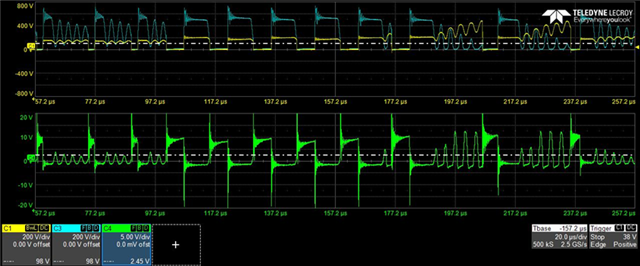

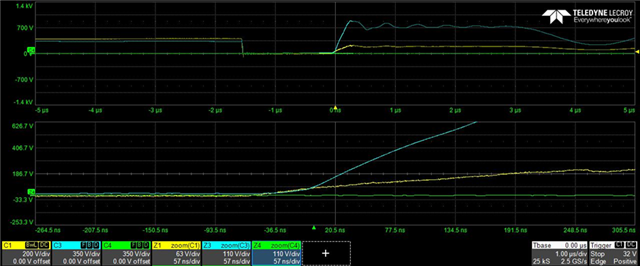

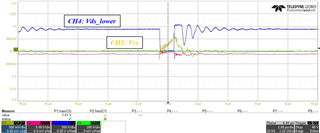

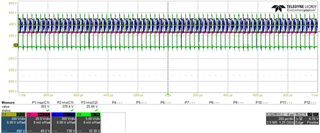

I followed the guide to create it, and I am currently testing it. So far, I have confirmed an output of 1 A with 600 Vdc input (refer to Figures 1 and 2). However, I have some concerns, so I cannot raise the voltage further in my experiment.

-

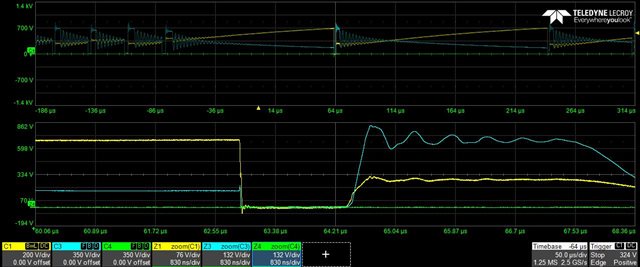

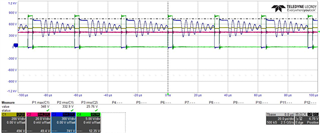

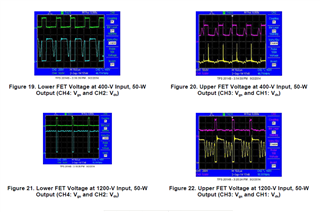

The document explains the following: At lower voltages (when upper switch Zener V < Vin), Figure 19 shows no ringing in Vds. However, in my experiment waveform, I see ringing (refer to Figure 3).

-

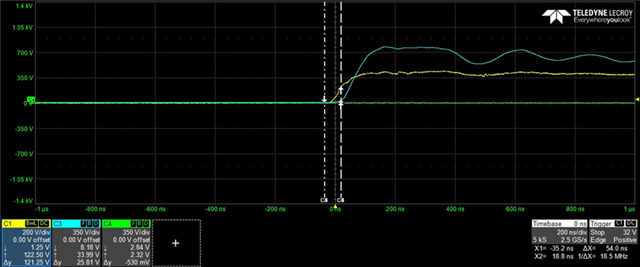

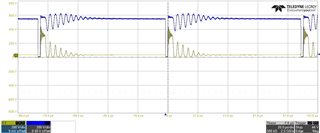

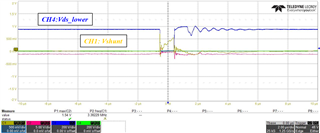

The SMPS designed according to the guide starts operating at 400 Vdc input, and this also happens in my experiment. However, when I connect the oscilloscope’s passive probe to measure the upper switch’s Vgs, the circuit operates at 300 Vdc input when it should not. Could this abnormal operation be due to the capacitance present in the oscilloscope’s passive probe? (Refer to Figures 4 and 5)

(CH1: D13 V, CH2: Vout, CH3: lower FET Vds, CH4: upper FET Vgs // Vin: 290 Vdc) -

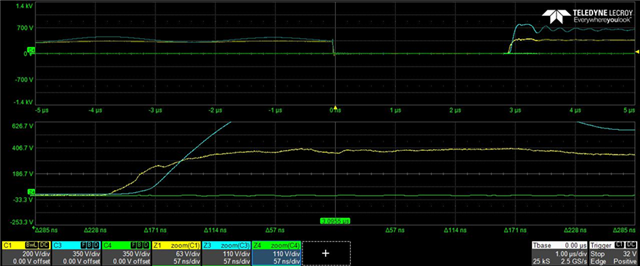

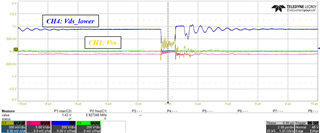

Nomarl operating condition, measuring upper switch Vgs by diffirential probe, test graph is Figure 5. There it looks like already turn on.because when lower swtich turn off, upper switch Vgs is 5~6V. i wonder it is measuring mistake or not. And I expected the Vgs to rise up to 12 V due to the parallel Zener diode being rated at 12 V. However, it only reaches 7-8 V. (Of course, I also confirmed in the guide document that the Vgs only reaches 7-8 V.)

-

Given the ringing on the lower FET and the observations from points 2 and 3, could it be that the upper FET is always turned on?

Fig.1 (CH1: D13 V, CH2: Vout, CH3: lower FET Vds, CH4: lower FET Vgs // Vin: 500Vdc)

Fig.2

(CH1: D13 V, CH2: Vout, CH3: lower FET Vds, CH4: lower FET Vgs // Vin: 500Vdc)

Fig.3 (CH1: D13 V, CH2: Vout, CH3: lower FET Vds, CH4: lower FET Vgs // Vin: 500Vdc)

Fig.4 CH1: D13 V, CH2: Vout, CH3: lower FET Vds, CH4: upper FET Vgs // Vin: 290 Vdc)

Fig.5 CH1: D13 V, CH2: Vout, CH3: lower FET Vds, CH4: upper FET Vgs // Vin: 290 Vdc).

when nomal condition, lower swtich Vds is below. sometime it dosen't have ringing and sometime have. I wonder it is why.