Tool/software:

Hi team,

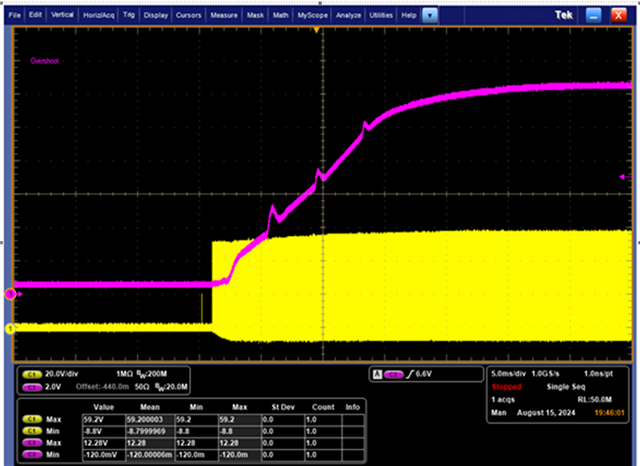

Customer tested the power on waveform of TPS54561. CH3 is vout, CH1 is SW. There are many bumps on Vout, could you please explain the reason? Could you please reproduce it on EVM?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi team,

Customer tested the power on waveform of TPS54561. CH3 is vout, CH1 is SW. There are many bumps on Vout, could you please explain the reason? Could you please reproduce it on EVM?

Hi Naizeng,

Can you please share the schematic and below data for further debug.

1. Input voltage [ min, typ, max]

2. output voltage and current

My suspect is, this could be due to frequency foldback effect that we have in TPS54561. A frequency foldback circuit reduces the switching frequency during start up and overcurrent fault conditions to help maintain control of the inductor current. Under startup light or no load condition, since the frequency is changing by 1/8th, 1/4th of RT frequency, there is possibility that overshoot could happen at the output node.

Thanks,

Nitya

Hi Nitya,

Input voltage is 54V, output voltage is 12V, max Iout 4.3A. fsw=450kHz, Tss=13.5mS.

Could you please test it on EVM?

Hi Naizeng,

Let me try on EVM about this behavior. Meantime if you share the schematic, it will help to debug further.

Thanks,

Nitya

Hi Nitya,

I know frequency foldback is critical for short circuit event. But for start up, I don't think it has any value because this device has soft start. So What's the funciton of frequency foldback during start up?

Hi Naizeng,

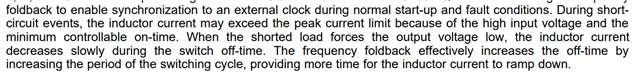

The frequency foldback is critical for both short circuit and startup operation. When output voltage is low during startup or heavy load condition, the device operates in lower duty cycle ratio to keep the inductor current within the range. Since the inductor current falling slope is very low during switch off time the minimum on-time limitation prevent the switcher from attaining a sufficiently low duty cycle at the programmed switching frequency. So, the switch current will keep increasing through each switch cycle, exceeding the programmed current limit. To prevent the switch peak currents from exceeding the programmed value frequency foldback is used during startup and short circuit conditions.

Thanks,

Nitya

Hi Nitya,

Could you please prepare a PPT document for customer including:

(1) the reason of this strange waveform

(2) the working mechanism of currend foldback and why we add it into this chip

(3) guarantee that this waveform will not affect the normal operation

Nison

Hi Nison,

Sure let me check internally and get back to you in couple of days.

BTW, who is the customer here?

Thanks,

Nitya

Hi Nitya,

Customer is Inspur, can you feedback by today? We cannot wait couple of days

Hi Nison,

Please see my comments below.

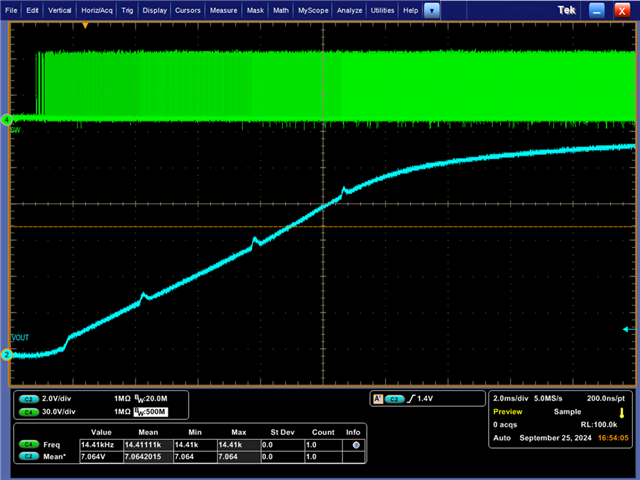

1. This is not strange waveform. This is expected during frequency transition from Fsw/2, Fsw/4, Fsw/8. This is tested on the EVM as well.

2. The theory of operation is briefly explained above.

3. The bump-up of the output voltage during frequency foldback is within the output voltage settings. It will not cause any issue during steady state operation.

Thanks,

Nitya