Tool/software:

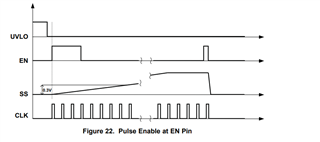

The datasheet describes how to "enter" pulse-enable operation by sending a falling edge to EN pin prior to SS reaching 0.3V. Great.

As the other posts imply there are concerns with 'accidental' glitches causing the IC to enter this pulse-enable operation. I understand methods to mitigate the concern.

But in the event that it does occur - how do we 'exit' pulse-enable mode to go back to level-enable? Does it require a Vdd UVLO to reset IC to level-enable mode? Please elaborate on how to exit pulse-enable mode, ideally without power cycling Vdd.