Tool/software:

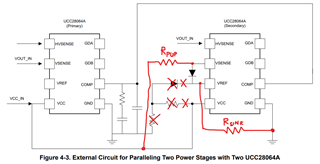

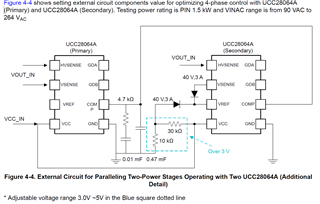

Hi, I'm looking at the SLUAAD0 application note on how to parallel two UCC28064A PFC controllers. I'm really confused by this part of the document...

The note implies we can adjust the resistive divider in the blue square to get between 3 and 5V from VCC - but what does this do? The other end of the diode is VREF, which is 6V, so will be reverse biased at all those voltage levels and so I can't work out what we're doing here.