Other Parts Discussed in Thread: UCC20225, TPS2838

Tool/software:

Hi,

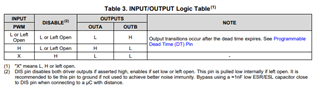

I want to use UCC20225 gate driver for the synchronous buck design. The design is 10:1 ratio. If the PWM duty cycle as input to the UCC20225, is 10%, would the other gate output become 90% (deadtime considered)? In other words, can I use this driver with below 50% duty?

If yes, how the will the controller knows if the pulse needs to be terminated already for the complimentary output if the controller does not have an information of switching frequency?

Thanks,

Ian