Tool/software:

Hello,

I'm having a couple of issues using the BQ25887 chip.

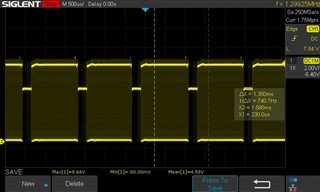

- The boost converter is unstable. Sometimes, seemingly randomly, the boost converter will work properly, but other times, switching will rapidly start and stop. If I lower the IINDPM register to around 1A, the converter is always stable.

- Whether the converter is currently operating normally or the instability mentioned above is occurring, the ICHG ADC register does not seem to be reading properly. When I see input currents around 2.5A and the converter is switching normally, and I am expecting to see the full 1.5A default charge current into the battery, I only see a very small charge current in the ICHG register that varies from 10mA to around 100mA. With lower currents, such as when I set the IINDPM to 1A, the ICHG values do seem to become more accurate, although still slightly lower than I would expect.

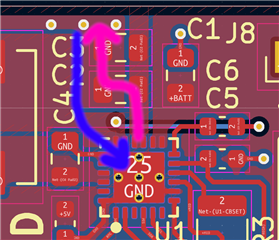

At this point I have become suspect of my PCB layout as the source of the stability issues, and am thinking that the innacurate charge current ADC value could be a symptom of the instability. I've ordered a BQ25887 EVM to see if I have the same issues on the reference hardware design. If I could get any support on confirming if the two issues are related or not, if the PCB layout is the likely cause, and what specifically about the layout needs to be improved if so, I would greatly appreciate it.

Here are the gerber files for the PCB:

Here is a screenshot of the SW node while the instability is occurring:

Here is a register dump while the instability is occuring:

Register Name: CELL_VOLTAGE_LIMIT, Address: 0, Value: A0

Register Name: CHARGE_CURRENT_LIMIT, Address: 1, Value: 5E

Register Name: INPUT_VOLTAGE_LIMIT, Address: 2, Value: 84

Register Name: INPUT_CURRENT_LIMIT, Address: 3, Value: 39

Register Name: PRECHARGE_AND_TERMINATION_CONTROL, Address: 4, Value: 22

Register Name: CHARGER_CONTROL_1, Address: 5, Value: 9D7D020D

Register Name: ICO_CURRENT_LIMIT, Address: A, Value: 18

Register Name: CHARGER_STATUS_1, Address: B, Value: 3B2

Register Name: NTC_STATUS, Address: D, Value: 0

Register Name: FAULT_STATUS, Address: E, Value: 0

Register Name: CHARGER_FLAG_1, Address: F, Value: 0

Register Name: FAULT_FLAG, Address: 11, Value: 0

Register Name: CHARGER_MASK_1, Address: 12, Value: 0

Register Name: FAULT_MASK, Address: 14, Value: 0

Register Name: ADC_CONTROL, Address: 15, Value: B0

Register Name: ADC_FUNCTION_DISABLE, Address: 16, Value: 0

Register Name: IBUS_ADC1, Address: 17, Value: B

Register Name: ICHG_ADC1, Address: 19, Value: 0

Register Name: VBUS_ADC1, Address: 1B, Value: 1185

Register Name: VBAT_ADC1, Address: 1D, Value: 1BF5

Register Name: VCELLTOP_ADC1, Address: 1F, Value: E60

Register Name: TS_ADC1, Address: 21, Value: 235

Register Name: TDIE_ADC1, Address: 23, Value: 5F

Register Name: PART_INFORMATION, Address: 25, Value: 29

Register Name: VCELLBOT_ADC1, Address: 26, Value: DCA

Register Name: CELL_BALANCING_CONTROL_1, Address: 28, Value: 2AF4

Register Name: CELL_BALANCING_STATUS_AND_CONTROL, Address: 2A, Value: C0

Register Name: CELL_BALANCING_FLAG, Address: 2B, Value: 0

Register Name: CELL_BALANCING_MASK, Address: 2C, Value: 0