Other Parts Discussed in Thread: UCC53X0S

Tool/software:

Hi,

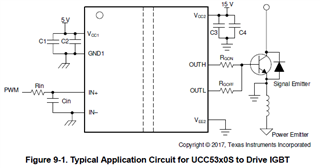

What are the limits for VEE2 for Split Outputs version (UCC53x0S)?

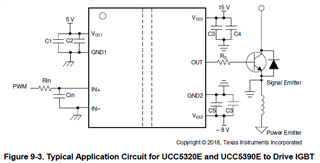

In the datasheet, it says from -17.5V to 0.3V (section 6.1). However, when I look at the Typical Application (section 9.1), the split outputs version (UCC53x0S) shows a VEE2 connected signal emitter.

Whille versions with UVLO referenced to GND2 (UCC53x0E) have VEE2 connected to negatiive rail.

Edit / update.

Even this datasheet shows two examples of negative bias, where Fig. 9-3 uses the split output model and VEE2 is tied to GND2, while Fig. 9-4 uses the Miller Clamp model, but the VEE2 is at negaive voltage.

Does that mean split output VEE2 must be connected to GND2 and cannot have negative voltage?

Kind regards, MB