Tool/software:

Hi,

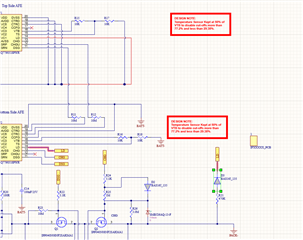

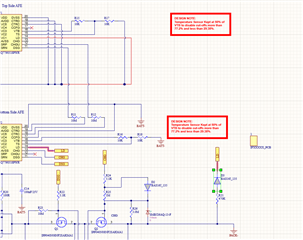

I am planning to use BQ7790518 for charging OV protection of a 8S battery pack. I have tied the LD pin of the top device to the local AVSS (top device ground). This disables the LD pin of the top device. However, for the bottom device, the LD pin is tied to a 470k resistor with a diode for protection against negative voltages at PACK-. Will my charge be detected by the LD pin in this configuration and the CHG FET will turn ON if my each CELL level voltage is in between 2.750V to 4.250V. What will happen to the LD PIN if an OV is detected? Will it clear automatically if I somehow reduce the cell voltage to less than 4.250V? Here is the schematic for your reference.