Other Parts Discussed in Thread: PMP40934

Tool/software:

I'm having trouble bringing up a custom board and would appreciate help diagnosing the fault. When connecting USB devices to the output the regulator immediately dies with a short across the input rail. Two different boards showed identical failures with CAQ parts, and an attempt with a CQ part also failed.

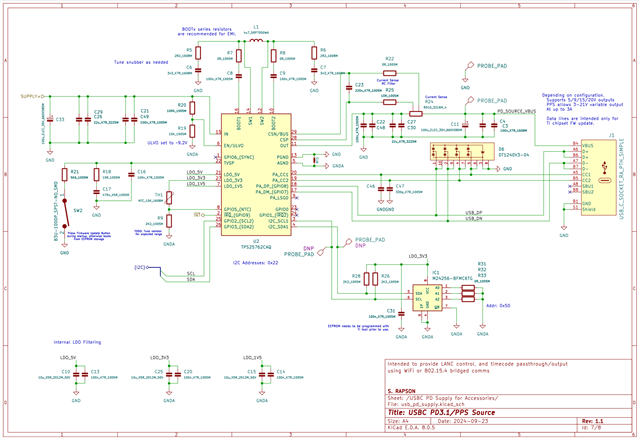

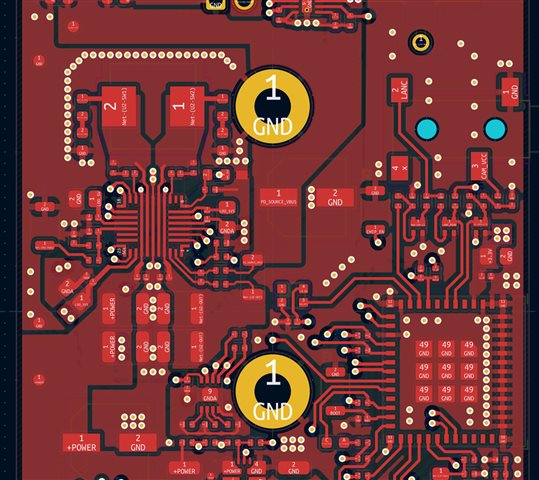

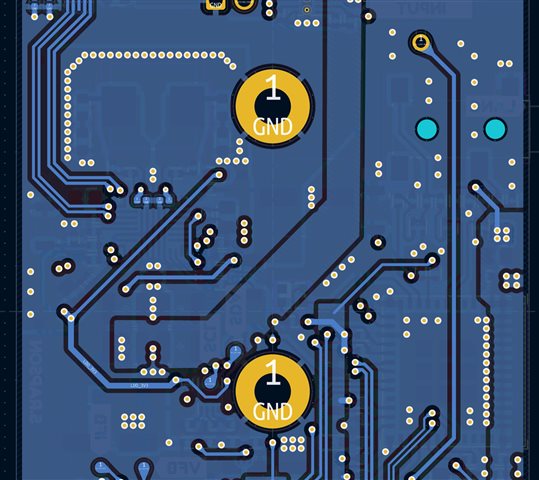

The relevant sections of the board design are attached for reference, with PDF and other relevant files in this Google Drive share.

I based the design on the datasheet reference, checked against the EVM and PMP40934 reference.

- I can't seem to attach the configuration json file, a copy (TPS25762CQ1_V8.01_09-12-2024_11-7-30.json) is in the shared GDrive folder.

- I manually flashed the EEPROM with a binary (base_lowregion_F311_guiCfg_5-9-58-36_full_flash.bin) generated with the GUI.

- Validated the flashed image by dumping and comparing and it seems OK, but

- because the binary is only 32128B, there are 640B at the end of the EEPROM which were left unwritten (0xFF).

Before connecting a USB device with the 2nd and 3rd attempts, I took a series of measurements (all with >6.5 digit SMU, truncated to relevant precision):

- Prior to failure, the input power rail has 40-70kΩ to GND.

- The USB VBUS net has >2MΩ to GND.

- Using a USBC breakout board, continuity tests pass for VBUS, GND, CC1/2, DP/DM pins.

- The input voltage is 12.05V,

- ULVO resistors are set in design to ~9.2V - for the 12V input, EN is at 1.55V which is within expected tolerance and above datasheet threshold,

- LDOs measured at the capacitors are at 1.55V, 3.52V and 4.65V which are within datasheet ranges,

- TVSP pin measures open to GND (>8MΩ measured due to capacitor/strays).

- SW1 and SW2 are ~4.2V,

- Output voltage (USB VBUS) is 0.35V.

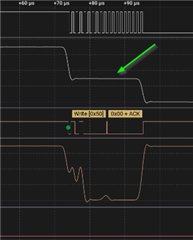

I captured the I2C traffic between the regulator and EEPROM during startup.

Transactions start ~480ms after 3V LDO is up, transactions seem fine with a quick look given there's no public docs on expected behaviour.

A Saleae Logic2 formatted save file is `tps25762-boot-eeprom-traffic.sal` in the shared folder, or I can pull specifics from the file as needed.

Notes on the failures:

- I am using low-cost hardware as first-test devices, a 12V 'decoy' barrel plug cable with no load, and a commodity cinema lens follow-focus motor capable of 5/9/12/15V.

- The TPS25762 fails immediately on connection. The test USB devices were undamaged.

- There is no visible damage to the part, no noise, and no heat during the fault (guessing the PCB's input OCP kicks in, unverified).

- After failure, the input power rail is shorted, ~0.08Ω. Removing the TPS25762 removes the short.

- Other circuitry on the PCB seems fine once the TPS25762 removed.

- I had a scope on the USB VBUS and input power rails for the most recent test/failure, but it didn't trigger so I have no waveform of the fault.

I have 2x TPS25762CAQ parts and 1x TPS25762CQ remaining, though without an electrical or possibly software configuration change I don't expect a different outcome.

Greatly appreciate any suggestions, a recommended bring-up procedure, or any voltage/waveforms to check which might help?