Tool/software:

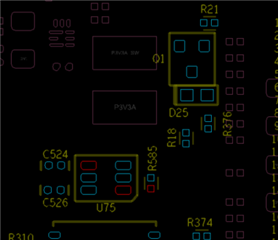

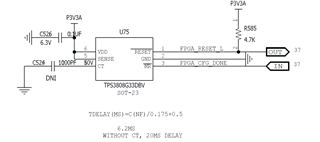

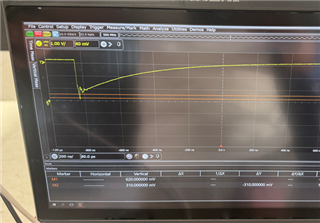

When I touch the FPGA_RESET_L with a bus wire, or a DVM probe, it will cause the signal to go down sharply and gradually rises up.

I probed MR_L while touching the reset_l with a wire, there is nothing on MR_L

P3V3A is also stable.

I put a 0.1uf on C524 and it doesn't help.

Have you seen anything like that? If I use a scope probe on reset_l, it's ok. I don't see this pulse. Only when I use a DVM meter probe or a jumper wire (AWG28), this happens.