Other Parts Discussed in Thread: , TPS25947EVM, TPS25947

Tool/software:

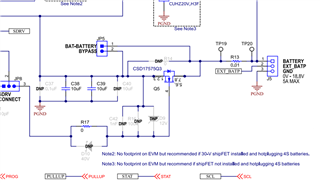

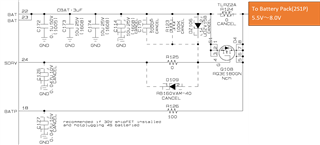

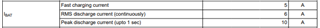

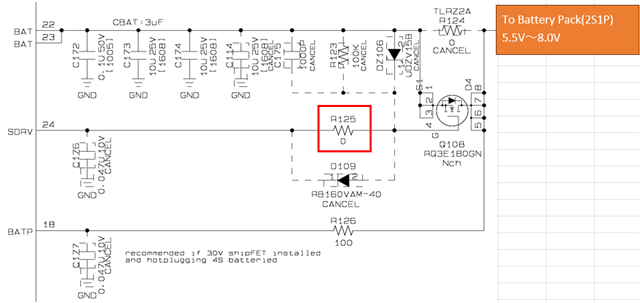

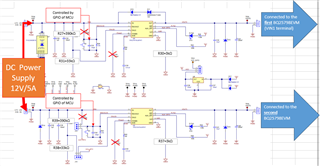

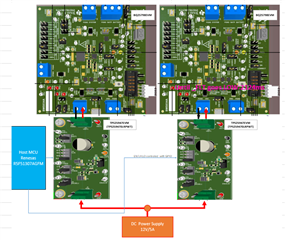

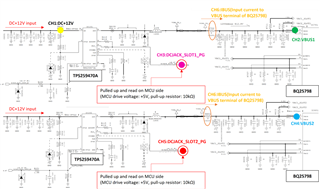

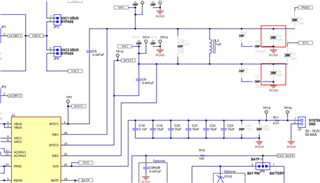

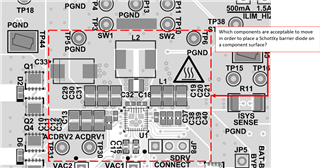

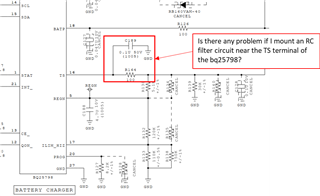

I would like to implement an RC filter circuit on the TS line of the bq25798 for ESD protection purposes. (R=100Ω, C=0.1μF)

I am considering the configuration shown in the attached circuit diagram, but if you have any concerns about this configuration, please let me know.

Regards,

Kagawa