Tool/software:

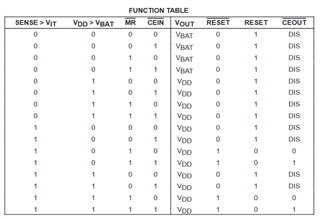

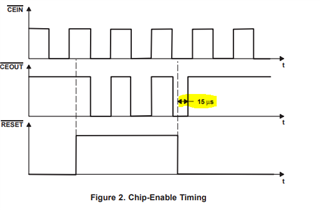

The table on page 2 of the datasheet implies the positive RESET output (pin 7) should be the opposite of the /RESET output all the time. The rest of datasheet implies these pins are always push-pull outputs.

However, in the case where SENSE is less than VIT, VDD is zero, and VBAT is 3V, the RESET output appears to be floating, not driven. As far as I can tell, though, the /RESET output is properly driven to GND.

Is this an error in the datasheet, or an error in the component? I have tried three separate parts for good measure, and all behave the same. (I would really like it to be a manufacturing error because I need that pin to be push-pull even when VDD is zero, though I'm not getting my hopes up)

Thank you.