Tool/software:

Hi,

I'm trying to understand the FAULT_IN pin's behaviour.

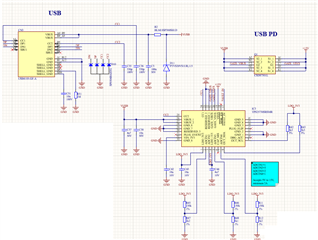

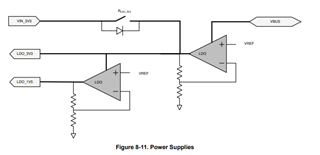

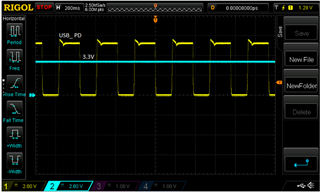

When the TPS25730 is supplied by 5V USB 2.0 source, the chip lets through the 5V even if the FAULT_IN pin is low. Is this normal behaviour? Also, once the FAULT_IN is set to HIGH and then set back to LOW, the TPS25730 does not cut-off the usb power to the internal circuit.

Thanks,

Tamas