Tool/software:

Hi Mike,

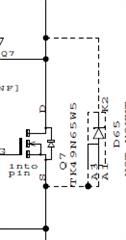

As per application note, and previous post, TABSET, TCDSET should be equal. SInce now we are using only fixed delay option. Adaptive delay is not being used as suggested.

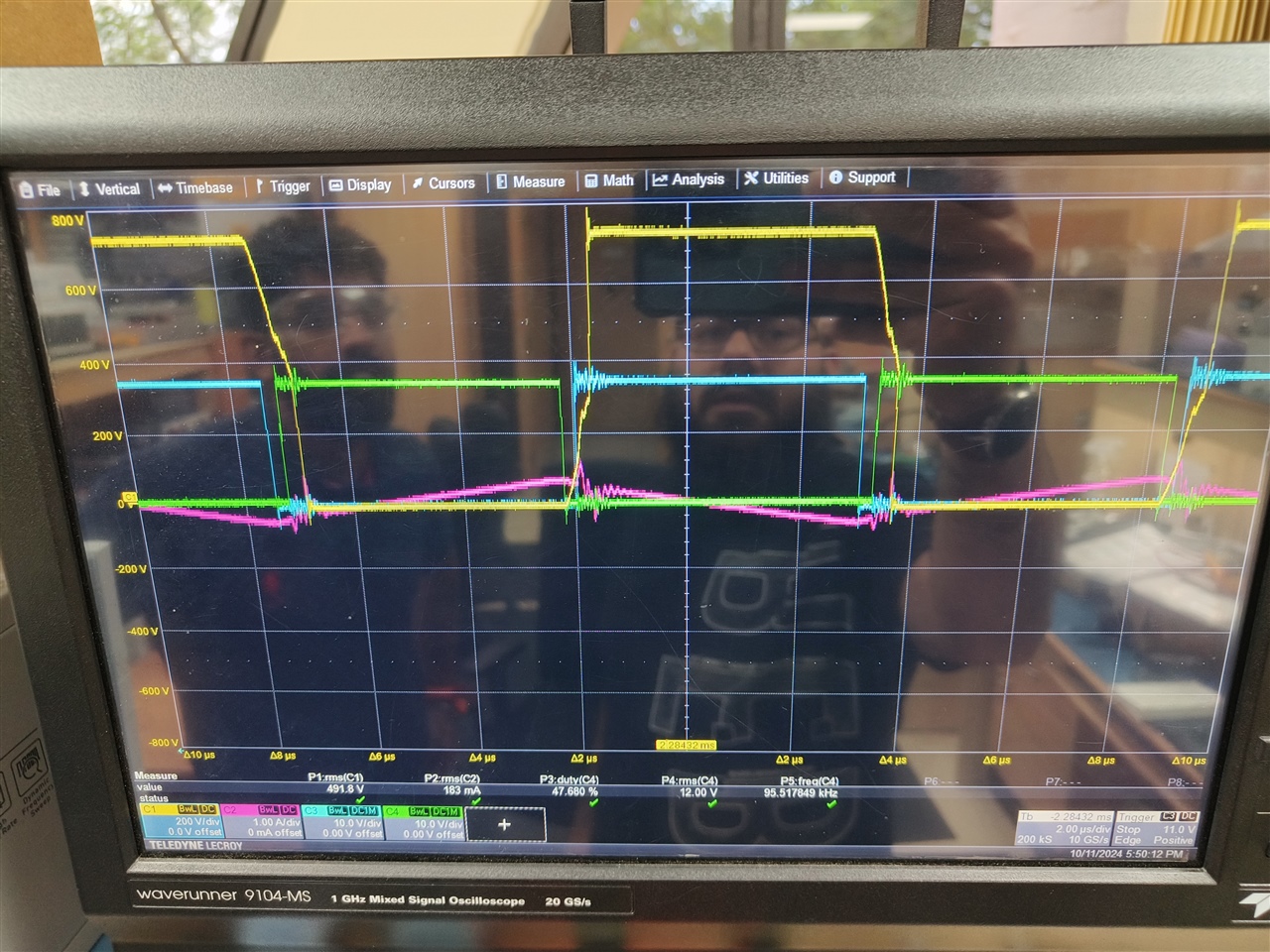

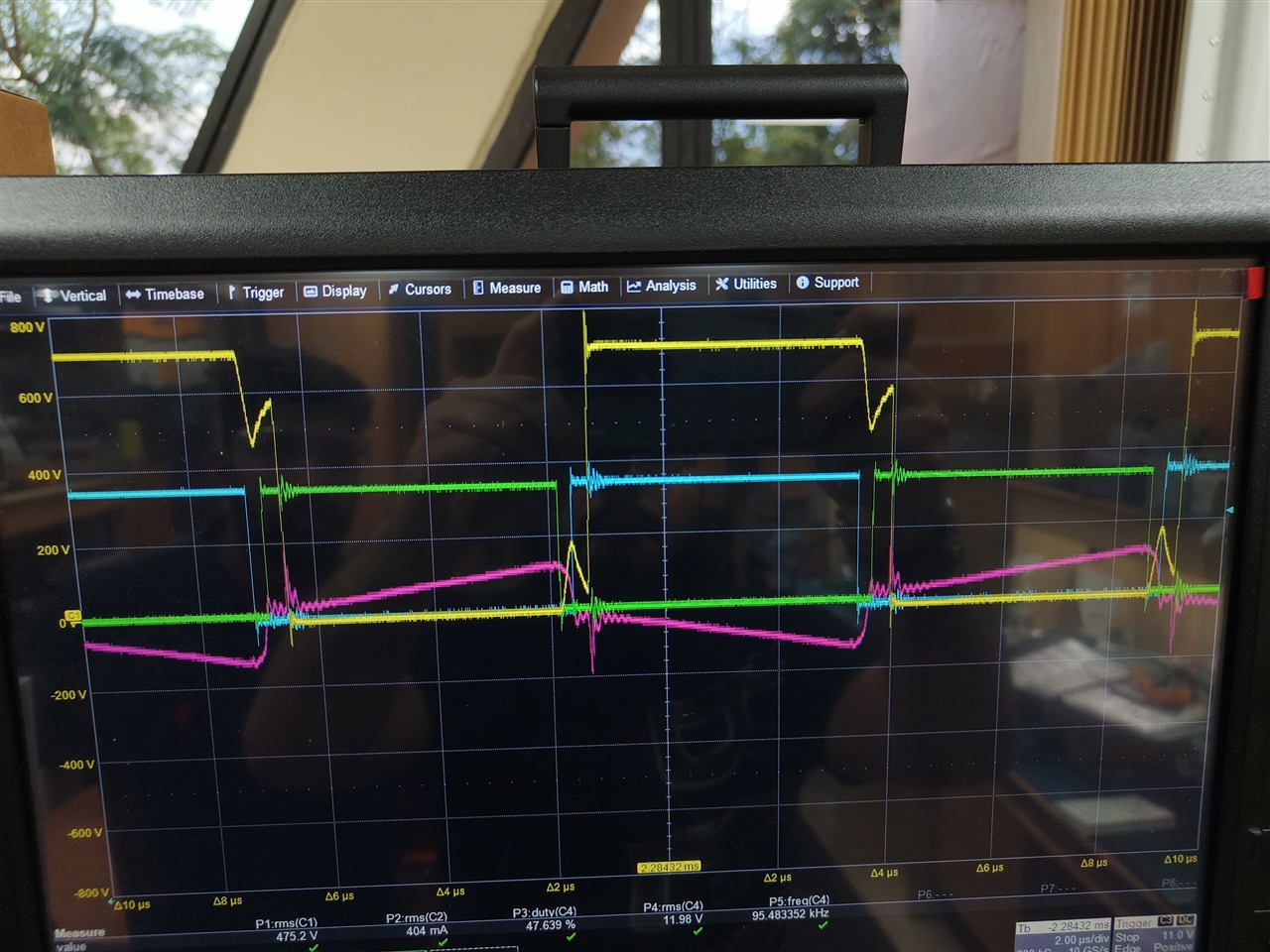

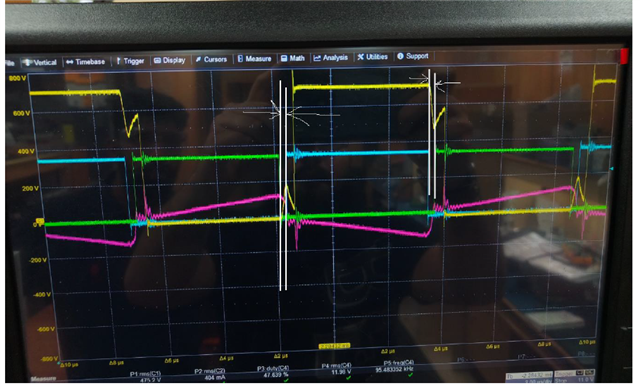

I have set more dead-time just to understand the issue. D Fet Turns OFF / turn ONN properly, coinciding with One of the synchronous gates( Blue ). Whereas B drain to source waveform if you observe, it tries to turn OFF / Turn ONN, but something is preventing it. Should I try adaptive delay option or should i continue with fixed delay option. Is it something to do with Leakage of transformer ? Kindly suggest.