Tool/software:

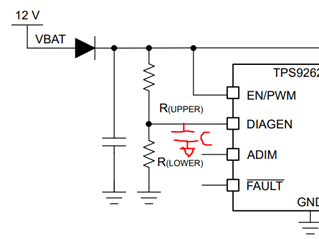

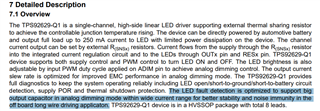

Hello I have a question regarding the TPS92629 Short to GND specification.

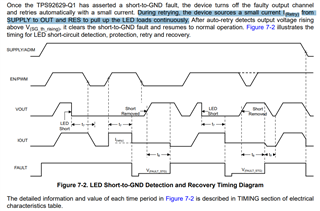

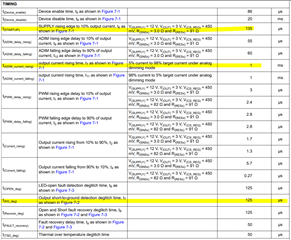

Short to GND deglith time defined at 125usec in the datasheet.

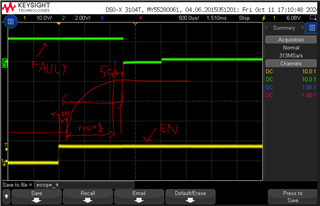

And I have concern of wrong detection at the start up.

Because if capacitive load is high and it takes more than 125usec to rise output voltage >1.24V, Wrong detection might be happened.

Does TPS92629 take preventive function of this situation ?