Tool/software:

Hello,Sir:

The PMIC we used is TPS6594133ARWERQ1, SoC is TDA4AL, and the power supply scheme we use is the J784S4 PDN-3F.

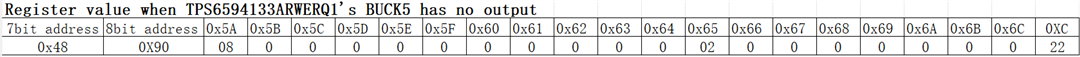

When the nPWRON/ENABLE pin low is less than about 10ms, BUCK5 has no output, but the other powers output is normal, and nRSTOUT is high,TDA4AL can not work,When there is a failure, the register value of BUCK5 is read, as shown in the figure.

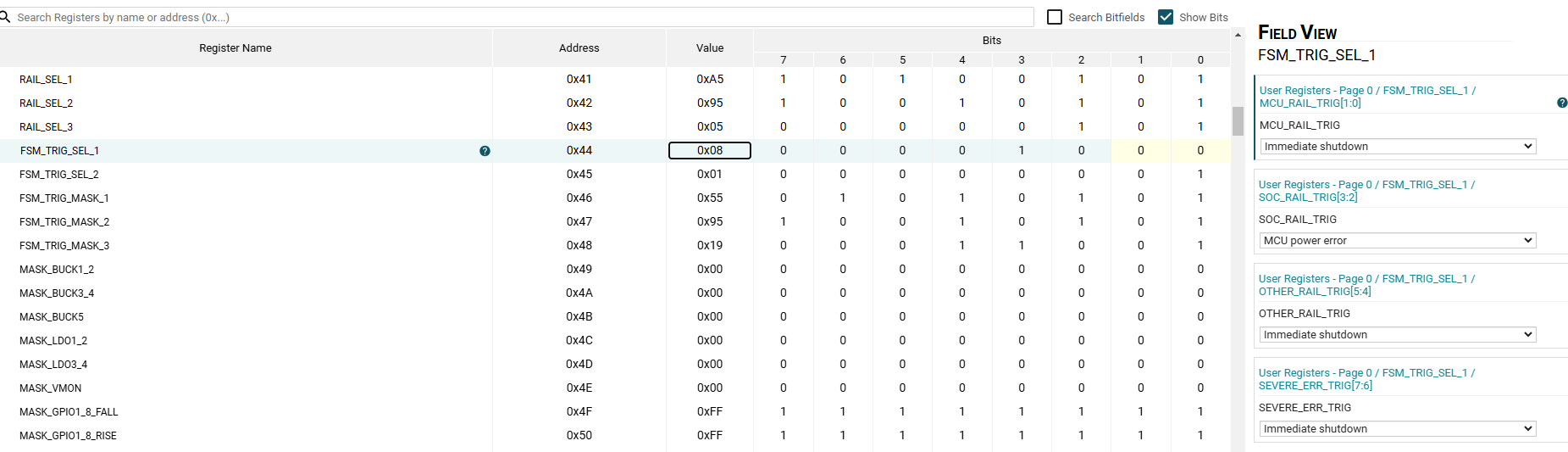

From the register value and the high level of nRSTOUT, it can be seen that PMIC actively shuts down BUCK5,which is not normal.

My questions are:

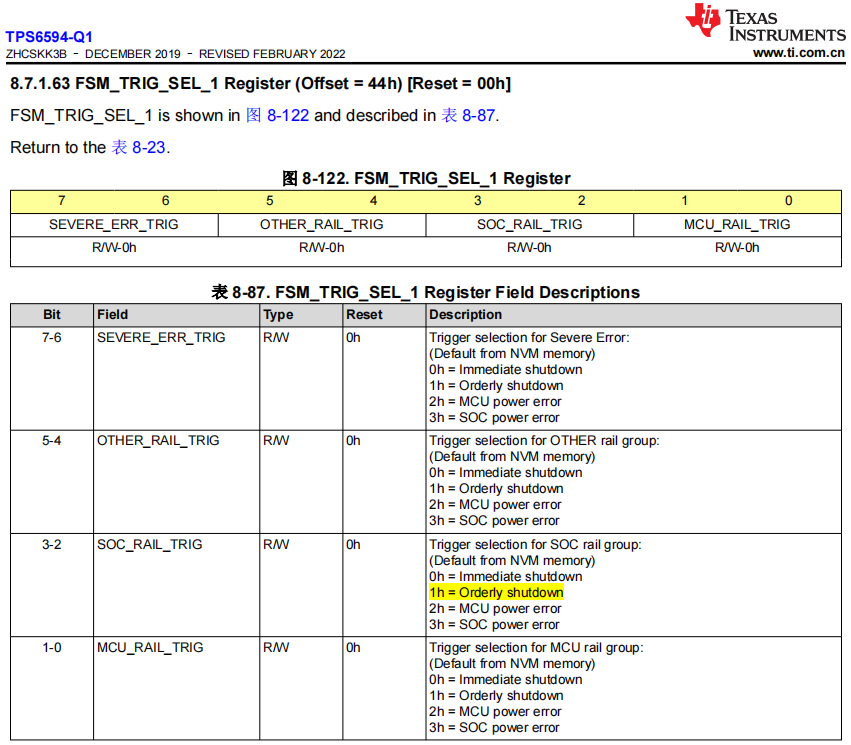

1.Why does this happen? Is NVM configured with some kind of action by default?

2.How to solve the question?