Other Parts Discussed in Thread: CSD95492QVM

Tool/software:

Hi,

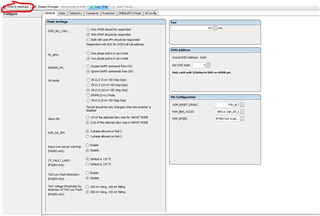

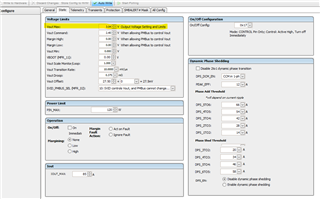

I have mentioned in earlier queries also. I have used TPS53659 SVID13 VR with Intel Xeon D1746 Processor.

Now, I am trying to program the VR with TI POWER FUSION DESIGNER GUI. where I am not able to set the VBOOT Value of Channel A (1.8V) or above 1.520V.

Please help me out with this.

Thank You

Raj Kumar