Tool/software:

hello,

we are using a Ucc28070A for an interleaved PFC with a mains input of 85-265Vac 47Hz-63Hz and an output of 385Vdc 2KW (5.2A). Switching frequency = 300kHz.

This one works correctly at 2KW up to a voltage of 255Vac, then from 255Vac to 265Vac, the top and bottom of the sinusoid of the input current is not "clean". At this moment an audible noise is generated by the boost inductors (Self planar of 70µH in our application). The voltage of the 385Vdc bus is still OK, it does not drop.

We thought it was the PKLMT that was acting but it is not the case (We increased the low resistance of the PKLIMIT divider bridge).

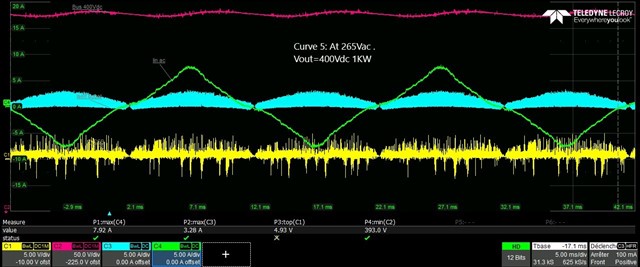

Then we increased the output voltage to 400Vdc to move away from the high rectified mains voltage but the fault remains the same. (See curves)

Then with an input voltage of 255Vac or 265Vac, we lowered the output power. The top and bottom of the sinusoid become correct again for an output power of 900-1000W!. (See curve)

Why do the top and bottom of this sinusoid have this shape despite moving away from the rectified mains voltage?

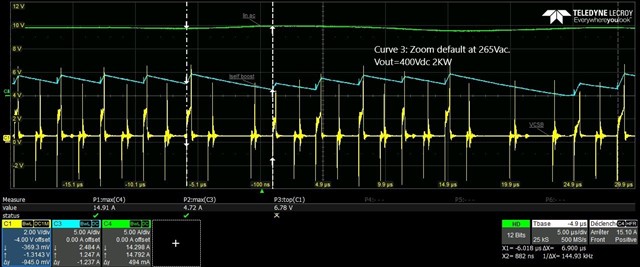

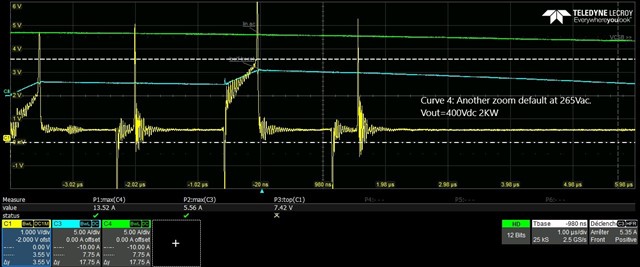

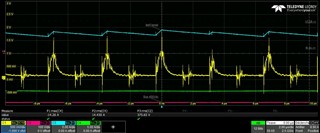

We noted curves with the bus at 385Vdc and at 400Vdc with the fault. All the curve zooms are taken at the peak of the current sinoid when there is the fault.

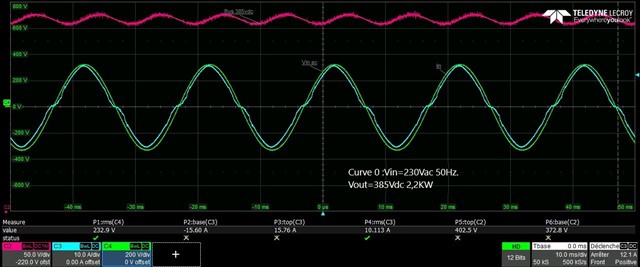

For curve 0: Red curve: Vout, Blue curve: Input phase current, Green curve: Vin=230Vac

Vin=230Vac Vout=385Vav 2KW

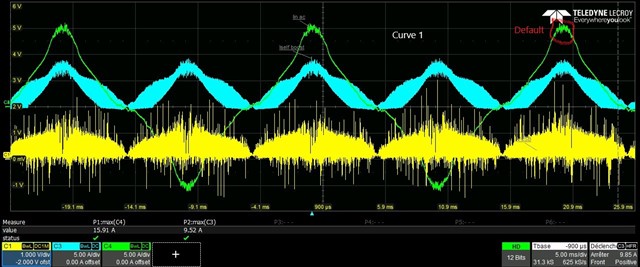

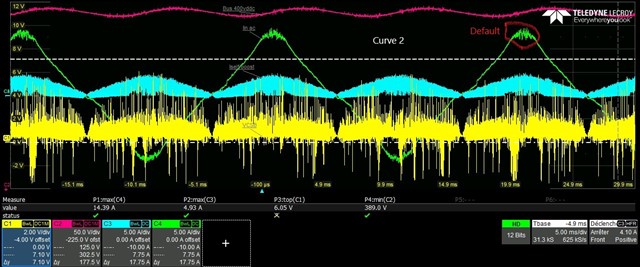

For another curves: Yellow curve: CSB voltage, red curve: Vout, blue curve: self boost B current, Green curve: Input phase current

Curve 1 Iin at 265Vac Vout 385Vdc 2KW

Curve 2 Iin at 265Vac Vout 400Vdc 2KW

Curve 3 Zoom default Iin at 265Vac Vout 400Vdc 2KW

Curve 4 Another zoom default Iin at 265Vac Vout 400Vdc 2KW

Curve 5 Iin at 265Vac Vout 400Vdc 1KW