Tool/software:

Hi

I would like to know if you think if this is part is suitable for what I tray to do. Below is spec

PCB dimension: 28mm x 30mm

PCB is a 4-layer board

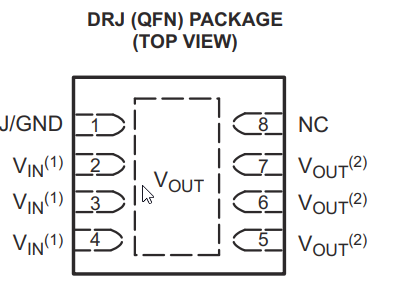

Part: TLV117-50CDRJR (QDFN)

Vin = 15

Vout = 5V

Output Current = 150mA (Max)

Thermal junction air = 38.2

T = (15-5)*0.15 * 38.2 = 82.45C

82.45 is lower than max temp wich is 125C.

Do you suggest using this part, or do you have alternative part with lower junction temp, or you suggest going with switching regulator.

Thanks