Hi,

I would like to ask a question on TPS65070 UVLO.

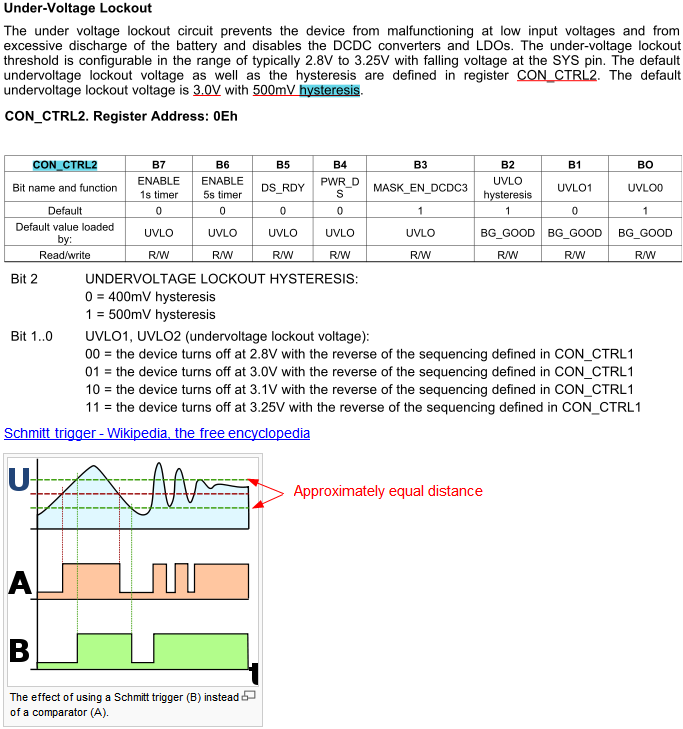

CON_CTRL2 could control both UVLO voltage and hysteresis. My question is how hysteresis is defined? For example, if bit[2] is made 1 and 500mV hysteresis is selected, does it mean ±250mV (±50%) around the UVLO voltage?

And if 400mV hysteresis is selected, does it mean ±200mV (±50%)?

I have little knowledge on Schmitt trigger, but I see on the Wikipedia page illustration that the green lines are approximately of equal distance from the red center line, so I suspect whether it is the same for UVLO hysteresis?

Another question is that is UVLO hysteresis implemented using Schmitt trigger? It seems that there can be a variety of ways for implementing it above at the elemental device (i.e., Schmitt trigger) level, such as maintaining internal registers values and doing comparison. What is the actual UVLO hysteresis implementation?

Zheng