Tool/software:

Hi,

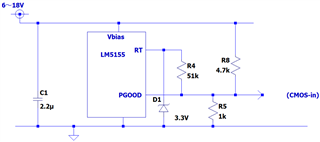

Could you please let me know if there is any information on the LM5155 PGOOD pin current rating? The datasheet states that "When VPGOOD > VBIAS, the maximum current sink is limited to 1mA," but this means that the current sink is limited to 1mA when the PGOOD pin is active. As I understand it, this is different from the absolute rating.

The background to the question is that with the current design, there is a possibility that about 5mA may flow to the PGOOD pin, and I would like to know if this will be a problem.

Thanks,

Conor