Tool/software:

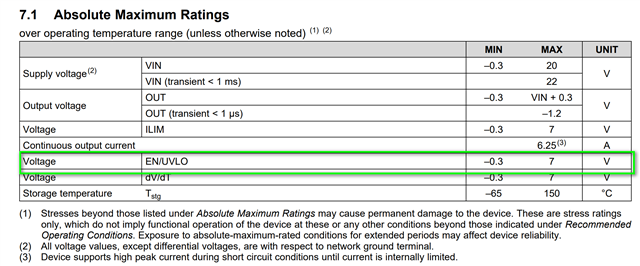

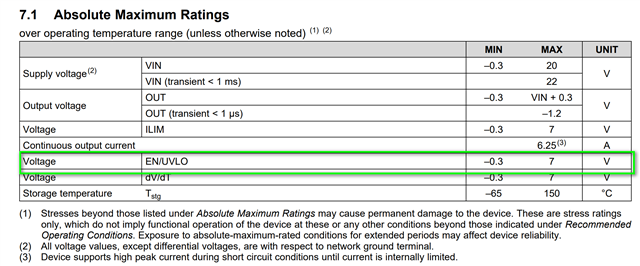

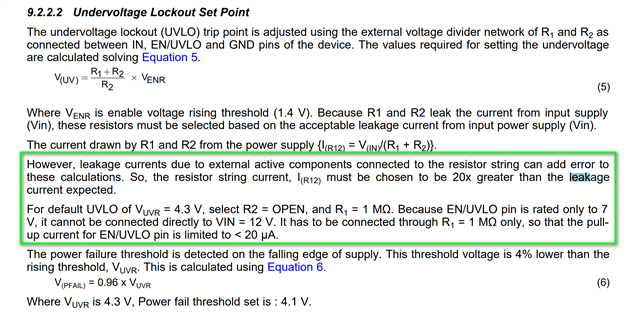

1、看手册要求EN/UVLO 是有最高7V的电平要求

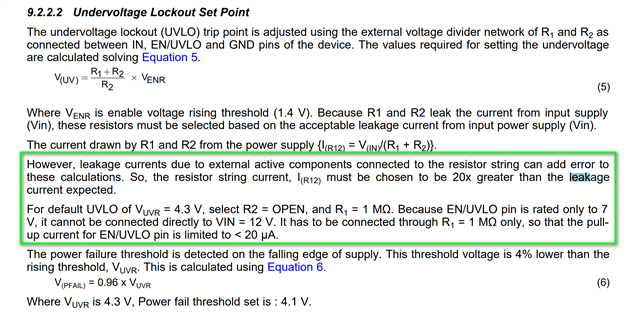

2、但是看设置欠压保护的描述,貌似也可以超过7V,只要电流保证即可,下面的参考设计就是R1设置成1M即可?

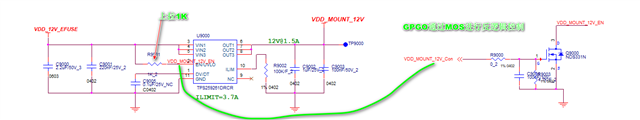

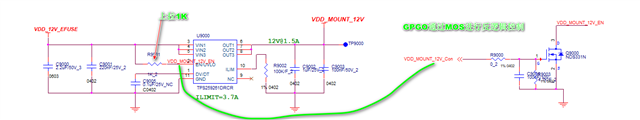

3、这个管脚的设置以哪个要求进行参考设计呢?如果以电流要求,电流最高要求多少呢,我们目前设计成下面的状况,发现也是OK的,帮忙看看这样设计是否存在风险

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

1、看手册要求EN/UVLO 是有最高7V的电平要求

2、但是看设置欠压保护的描述,貌似也可以超过7V,只要电流保证即可,下面的参考设计就是R1设置成1M即可?

3、这个管脚的设置以哪个要求进行参考设计呢?如果以电流要求,电流最高要求多少呢,我们目前设计成下面的状况,发现也是OK的,帮忙看看这样设计是否存在风险

Hi Dang Jinfa,

1、看手册要求EN/UVLO 是有最高7V的电平要求

Yes, trhis pin should not get voltage higher than 7V.

2、但是看设置欠压保护的描述,貌似也可以超过7V,只要电流保证即可,下面的参考设计就是R1设置成1M即可?

Here we also have pull down resistor so the voltage at the pin won't cross 7V.

3、这个管脚的设置以哪个要求进行参考设计呢?如果以电流要求,电流最高要求多少呢,我们目前设计成下面的状况,发现也是OK的,帮忙看看这样设计是否存在风险

There are some risk in this when the FET is off, the EN pin will get 12V which violate the maximum limit. Can you use a resistive ladder from vin to GND to provide the necessary voltage to the EN pin. You can also connect the FET for active pull down.

Best Regards,

Arush

Hi Dang,

No, we don't have internal pull down in the device. I see that in the EVM, the pull down is DNP. I am not sure the reason for DNP in the EVM but this pulldown is necessary for higher voltage testing. In EVM, we do have placeholder for the pull down so that you connect the desired resistive ladder according to the desired voltage rail.

Best Regards,

Arush

Yes, the pull-down resistor on the EVM is DNP. When the input is 12V, but with a pull-up resistor of 1M ohms and the pull-down resistor DNP (Do Not Place), I tested the voltage of that pin and it was around 6V. I don't quite understand why with a 1M ohm pull-up resistor and an pull-down DNP, thePIN logic level is not 12V but 6V?

Hi Dang,

I am not fully sure about why this is happening on EVM. But atleast in your design please use pull down so that abs max violation do not happen.

Best Regards,

Arush